#### **Learning Objectives**

After completing this chapter you, will learn the following:

- Frequency response of amplifiers.

- h-parameter model of amplifiers.

- h-parameter model of BJT amplifiers.

- Analysis of different BJT amplifier configurations using h-parameters.

- Small signal response of FET amplifiers.

- Cascading amplifiers.

- Darlington amplifiers.

- Cascode amplifiers.

- Low-frequency response of BJT amplifiers.

- Low-frequency response of FET amplifiers.

- Effect of cascading amplifier stages on the overall frequency response.

The chapter focuses on the small signal response of BJT and FET amplifiers. The small signal response of BJT amplifiers is mostly analyzed using the h-parameter model. In the chapter, the h-parameter model for the three BJT configurations is covered and detailed analysis of BJT amplifiers using the h-parameter model has been carried out. The small signal response of FET amplifiers is also discussed. In addition to the mid-band analysis, the low-frequency response of both BJT and FET amplifiers is also discussed in the chapter.

Cascading of amplifiers is done to increase the value of gain, to match the input and output impedances of the amplifier with the source and the load impedance, respectively. Cascading of BJT and FET amplifiers with particular reference to its effect on the overall frequency response of the amplifier is also described. Other topics covered in the chapter include Darlington amplifiers and Cascode amplifiers.

# 8.1 Amplifier Bandwidth: General Frequency Considerations

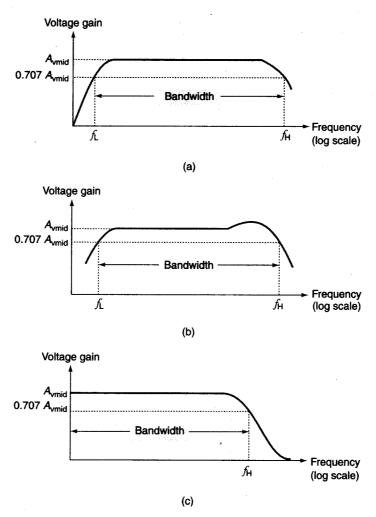

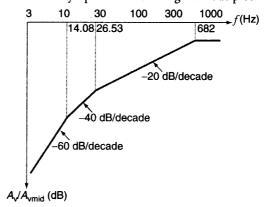

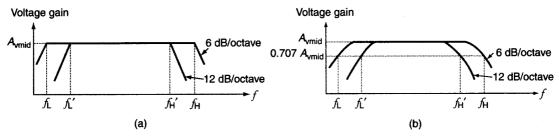

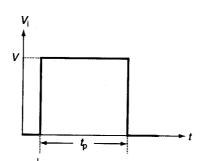

The response of an amplifier to an input signal depends upon the frequency of the signal. Figure 8.1 shows the typical frequency response curves for the RC-coupled, transformer-coupled and the direct-coupled amplifiers. The horizontal scale is a logarithmic scale to permit the plot to highlight both the low-frequency and the high-frequency regions of the response curve. For each curve three regions have been defined, namely, the low-frequency region, the mid-frequency region and the high-frequency region.

**Figure 8.1** (a) Typical frequency response curve of RC-coupled amplifier; (b) typical frequency response curve of transformer-coupled amplifier; (c) typical frequency response curve of direct-coupled amplifier.

Low-frequency response of an amplifier is affected by the input and the output coupling capacitors and the bypass capacitors. At low frequencies, these capacitors cannot be replaced by short-circuit approximations as their reactances increase at low frequencies. The stray capacitances and the capacitive elements related to the active device and the network limit the high-frequency response of the system.

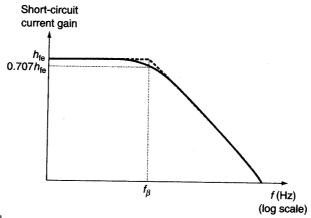

For each amplifier there is a region of frequencies where the magnitude of gain is relatively close to the mid-band value. The cut-off levels are defined by the frequencies where the gain value in decibels falls below the mid-band value by 3 decibels. In other words, the cut-off frequencies are defined as those frequencies where the magnitude of the gain in 0.707 times its value at the mid-band frequencies or the magnitude of the power gain is half of the magnitude of the power gain at the mid-band frequencies. The cut-off frequencies are referred to as the lower cut-off frequency ( $f_{\rm L}$ ) and the upper cut-off frequency ( $f_{\rm H}$ ). The difference between the upper cut-off and the lower cut-off frequencies is referred to as the bandwidth of the system.

### 8.2 Hybrid h-Parameter Model for an Amplifier

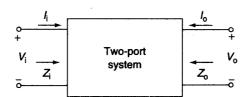

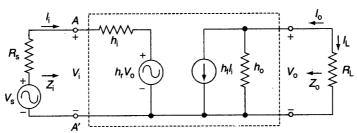

A two-port, four-terminal device or an amplifier (Figure 8.2) with two input and two output terminals can be represented in terms of an equivalent circuit model making use of two currents and two voltages provided that it meets the following two conditions. First, there is a common connection between the input and the output. Second, it should contain only linear elements. Two of the four variables (input and output currents, input and output voltages) can be chosen as the independent variables and the remaining two variables can be expressed in terms of these independent variables. The choice of the independent variables depends upon the nature of the device.

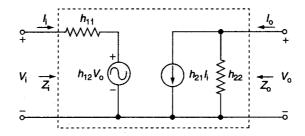

Transistors are generally modeled using the hybrid parameter model or the h-parameter model and the transistor datasheets provide the values of the h-parameters. Hence, the hybrid parameter model is described here in detail. In the case of h-parameter model, input current  $(I_i)$  and output voltage  $(V_o)$  are taken as independent variables. The other two variables, namely, the input voltage  $(V_i)$  and the output current  $(I_o)$  are related to these variables by the following equations:

$$V_{i} = h_{11}I_{i} + h_{12}V_{0} \tag{8.1}$$

$$I_0 = h_{21}I_1 + h_{22}V_0 (8.2)$$

The quantities  $h_{11}$ ,  $h_{12}$ ,  $h_{21}$  and  $h_{22}$  are referred to as the hybrid parameters or the h-parameters. The term "hybrid" is chosen as these terms have different dimensions, that is, they are not alike dimensionally. Figure 8.3 shows the representation of the network in terms of the h-parameters. As we can see from the figure, the h-parameter model makes use of the Thevenin's voltage equivalent model at the input and the Norton's current equivalent model at the output. It may be mentioned here that  $V_i$  and  $I_i$  are the RMS voltage and current values, respectively, of the applied input signal.  $V_o$  and  $I_o$  are the RMS voltage and current values of the resulting output signal.

Figure 8.2 Block diagram of a two-port, four-terminal device.

Figure 8.3 | h-parameter model of a two-port network.

#### **Determination of h-Parameters**

1. Parameter  $b_{11}$ : In Eq. (8.1), substituting  $V_0 = 0$ , that is, the output terminals are short circuited, we get

$$b_{11} = \frac{V_i}{I_i} \bigg|_{V_i = 0} \tag{8.3}$$

where  $V_i$  and  $I_i$  are the RMS values of input voltage and current, respectively. Using partial calculus, the value of  $h_{11}$  can be calculated as

$$b_{11} = \frac{\partial v_i}{\partial i_i} \bigg|_{V_o = \text{ const.}} = \frac{\Delta v_i}{\Delta i_i} \bigg|_{V_o = \text{ const.}}$$

(8.4)

Therefore, the parameter  $h_{11}$  is the ratio of the instantaneous change in the input voltage to the instantaneous change in the input current for constant value of output voltage. Hence, the parameter  $h_{11}$  has the units of impendance, that is, ohms. It is referred to as the short-circuit input impedance parameter. The subscript 11 indicates that it is dependent on the values of the input quantities.  $h_{11}$  is also represented as  $h_{11}$ .

2. Parameter  $b_{12}$ : In Eq. (8.1), if we substitute  $I_i = 0$ , that is, the input terminals are open circuited, then

$$h_{12} = \frac{V_{i}}{V_{o}} \bigg|_{I_{i} = 0} \tag{8.5}$$

Using partial calculus, the value of  $b_{12}$  can be determined as

$$h_{12} = \frac{\partial v_i}{\partial v_o}\Big|_{I_i = \text{ const.}} = \frac{\Delta v_i}{\Delta v_o}\Big|_{I_i = \text{ const.}}$$

(8.6)

Here  $h_{12}$  is the ratio of the instantaneous change in the input voltage to the instantaneous change in the output voltage for constant value of input current and is referred to as the open-circuit reverse transfer voltage ratio parameter. It is a dimensionless quantity.  $h_{12}$  is also represented as  $h_r$ .

3. Parameter  $h_{21}$ : If in Eq. (8.2), we substitute  $V_0 = 0$ , that is, the output terminals are shorted, then

$$h_{21} = \frac{I_o}{I_i} \bigg|_{V=0} \tag{8.7}$$

Applying partial calculus, the value of  $h_{21}$  is given by

$$h_{21} = \frac{\partial i_{o}}{\partial i_{i}}\Big|_{V_{o} = \text{const.}} = \frac{\Delta i_{o}}{\Delta i_{i}}\Big|_{V_{o} = \text{const.}}$$

(8.8)

Parameter  $h_{21}$  is the ratio of the change in the instantaneous value of output current to the change in the instantaneous value of the input current for constant value of output voltage. It is dimensionless parameter and is referred to as the short-circuit forward transfer current ratio parameter.  $h_{21}$  is also represented as  $h_{\rm f}$ .

4. Parameter  $b_{22}$ : If the input terminals are open circuit, that is,  $I_i = 0$ , then Eq. (8.2) simplifies to

$$h_{22} = \frac{I_o}{V_o} \bigg|_{I_c = 0} \tag{8.9}$$

Applying partial calculus we get

$$h_{22} = \frac{\partial i_{o}}{\partial v_{o}} \bigg|_{I_{c} = \text{const.}} = \frac{\Delta i_{o}}{\Delta v_{o}} \bigg|_{I_{c} = \text{const.}}$$

(8.10)

Parameter  $h_{22}$  is the ratio of the change in the instantaneous value of output current to the change in the instantaneous value of the output voltage for constant value of input current. It is referred to as the open-circuit output admittance parameter and is measured in siemens.  $h_{22}$  is also represented as  $h_0$ .

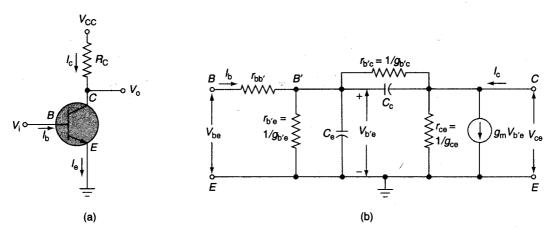

# 8.3 Transistor Hybrid Model

The h-parameter model is widely used for bipolar junction transisters. The basic assumption here is that the variations in the Q-point are small, so that the transistor parameters can be considered constant over the complete signal excursion. It may be mentioned here that the h-parameter model is applicable to all the three transistor configurations. The values of h-parameters are more or less constant for a given transistor, although they vary slightly with change in collector current. However, they have different values for each of the three transistor configurations. In this section we discuss the h-parameter model for the three transistor configurations.

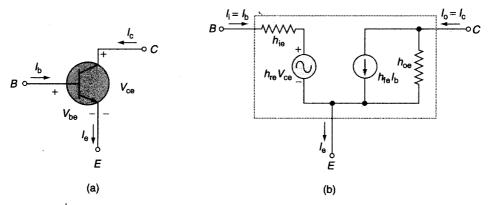

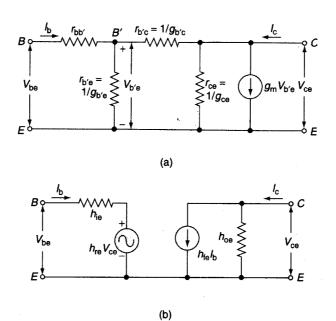

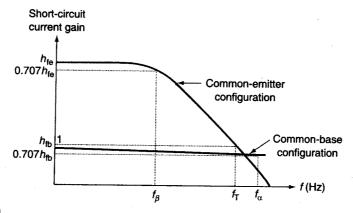

#### h-Parameter Model for the Common-Emitter Configuration

Figures 8.4(a) and (b) show the circuit symbol and the h-parameter equivalent model for the common-emitter configuration, respectively. As we can see from the figure, a second subscript has been added to the nomenclature of the h-parameters. This is done so as to distinguish between the h-parameters of the three transistor configurations. The parameter  $h_{11}$  is denoted as  $h_{ie}$  and is referred to as the input impedance of the transistor in the common-emitter configuration. Parameter  $h_{21}$  is denoted as  $h_{fe}$  and stands for forward current transfer ratio for the common-emitter transistor configuration; parameter  $h_{12}$  is denoted as  $h_{re}$  and is referred to as the reverse voltage transfer ratio for the common-emitter transistor configuration. Parameter  $h_{22}$  is denoted as  $h_{oe}$  and it means the output admittance for the common-emitter configuration. Note that in this case, current  $I_{o}$  is the base current  $I_{o}$  is the collector current  $I_{c}$ , voltage  $V_{i}$  is the voltage  $V_{be}$  and voltage  $V_{o}$  is the voltage  $V_{ce}$ . The h-parameter equations for the common-emitter configuration are given by the following two equations:

$$V_{bc} = h_{ic}I_{b} + h_{rc}V_{cc}$$

(8.11)

$$I_c = h_{\rm fe}I_{\rm h} + h_{\rm or}V_{\rm cc} \tag{8.12}$$

Figure 8.4 (a) Circuit symbol of common-emitter transistor configuration; (b) h-parameter model for the common-emitter transistor configuration.

The values of the parameters  $h_{ie}$ ,  $h_{fe}$ ,  $h_{re}$  and  $h_{oe}$  are given by the following set of equations, respectively.

$$h_{ie} = \frac{\partial v_{be}}{\partial i_b} \bigg|_{V_{\alpha} = \text{const.}} = \frac{\Delta v_{be}}{\Delta i_b} \bigg|_{V_{\alpha} = \text{const.}}$$

(8.13)

$$h_{\rm re} = \frac{\partial v_{\rm bc}}{\partial v_{\rm ce}} \bigg|_{I_{\rm b} = \text{ const.}} = \frac{\Delta v_{\rm bc}}{\Delta v_{\rm ce}} \bigg|_{I_{\rm b} = \text{ const.}}$$

(8.14)

$$b_{\rm fe} = \frac{\partial i_{\rm c}}{\partial i_{\rm b}} \bigg|_{V_{\rm cc} = \text{const.}} = \frac{\Delta i_{\rm c}}{\Delta i_{\rm b}} \bigg|_{V_{\rm cc} = \text{const.}}$$

(8.15)

$$h_{\text{oe}} = \frac{\partial i_{\text{c}}}{\partial \nu_{\text{ce}}} \Big|_{I_{\text{b}} = \text{const.}} = \frac{\Delta i_{\text{c}}}{\Delta \nu_{\text{ce}}} \Big|_{I_{\text{b}} = \text{const.}}$$

(8.16)

The symbol  $\Delta$  refers to a small variation around the quiescent point of operation, that is, the h-parameters are determined in the region of operation for the applied signal. The effect of the parameter  $h_{\rm re}$  is so small on the transistor amplifier that it can be neglected. Figure 8.5 shows the simplified h-parameter model for the common-emitter transistor configuration. Here,  $h_{\rm re}$  is assumed to be zero, therefore the magnitude of the voltage source  $h_{\rm re}V_{\rm ce}$  is also equal to zero. In other words, it results in short-circuit equivalent for the feedback element. In cases where the value of  $1/h_{\rm oe}$  is very large as compared to the value of load resistance, it is assumed to be open in comparison with the parallel load to be connected across the output terminals.

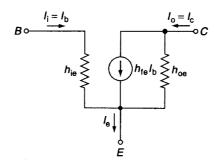

Figures 8.6(a), (b) and (c) respectively show the circuit symbol, complete h-parameter model and simplified h-parameter model of the common-collector configuration. The parameter  $h_{ic}$  is referred to as the input impedance of the transistor in the common-collector configuration. Parameter  $h_{fc}$  stands for forward current transfer ratio for the common-collector configuration and parameter  $h_{rc}$  is referred to as the reverse voltage transfer ratio for the common-collector configuration. Parameter  $h_{oc}$  is the output admittance in the common-collector configuration. The h-parameters for the common-collector configuration can be determined in a similar fashion as that for the common-emitter configuration.

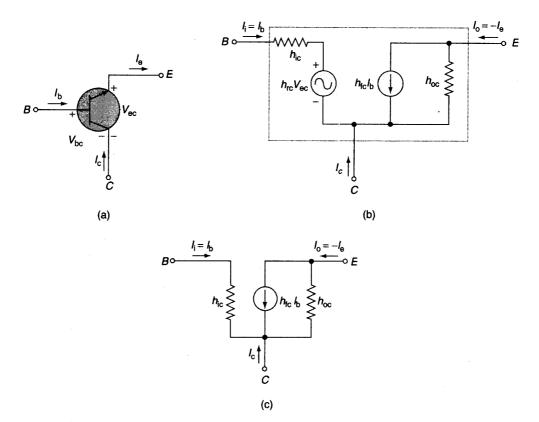

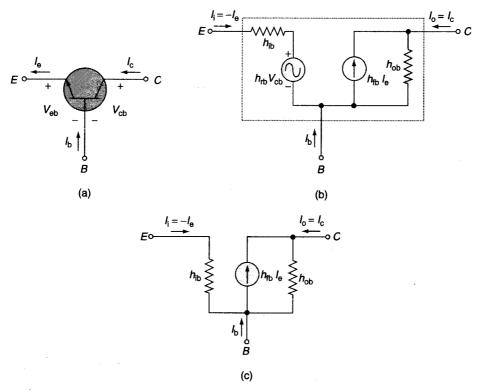

Figures 8.7(a), (b) and (c) respectively show the circuit symbol, complete h-parameter model and the simplified h-parameter model for the common-base configuration.  $h_{\rm ib}$  is the input impedance parameter,  $h_{\rm fb}$  is the forward current transfer ratio,  $h_{\rm rb}$  is the reverse voltage transfer ratio and  $h_{\rm ob}$  is the output admittance parameter for the common-base configuration.

Figure 8.5 | Simplified h-parameter model for the common-emitter transistor configuration.

Figure 8.6 | Common-collector transistor configuration: (a) Circuit symbol; (b) h-parameter model; (c) simplified h-parameter model.

#### Relationships between h-Parameters of Different Transistor Configurations

While designing a transistor-based amplifier, it may be necessary to convert from one set of transistor's h-parameters of a given configuration to another for the other configurations. Table 8.1 gives the approximate conversion formulae for the h-parameters. Derivation of the formulae is beyond the scope of the book.

Table 8.1

Approximate conversion formulae for the h-parameters

| $b_{\rm ic} = b_{\rm ie}$                        | $b_{\rm rc} = 1$                                                        | $b_{\rm fc} = -(1 + b_{\rm fe})$                  | $h_{\rm oc} = h_{\rm oe}$                        |

|--------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|

| $h_{\rm ib} = \frac{h_{\rm ic}}{1 + h_{\rm fc}}$ | $h_{\rm rb} = \frac{h_{\rm ie}h_{\rm oc}}{1 + h_{\rm fe}} - h_{\rm re}$ | $h_{\rm fb} = -\frac{h_{\rm fe}}{1 + h_{\rm fe}}$ | $h_{\rm ob} = \frac{h_{\rm oe}}{1 + h_{\rm fe}}$ |

| $h_{\rm ie} = \frac{h_{\rm ib}}{1 + h_{\rm fb}}$ | $h_{\rm re} = \frac{h_{\rm ib}h_{\rm ob}}{1 + h_{\rm fb}} - h_{\rm rb}$ | $h_{\rm fe} = -\frac{h_{\rm fb}}{1 + h_{\rm fb}}$ | $b_{\rm oe} = \frac{b_{\rm ob}}{1 + b_{\rm fb}}$ |

| $h_{\rm ic} = \frac{h_{\rm ib}}{1 + h_{\rm fb}}$ | $b_{\rm rc} = 1$                                                        | $h_{\rm fc} = -\frac{1}{1 + h_{\rm fb}}$          | $b_{\rm oc} = \frac{b_{\rm ob}}{1 + b_{\rm fb}}$ |

Figure 8.7 | Common-base transistor configuration: (a) Circuit symbol; (b) h-parameter model; (c) simplified h-parameter model.

#### **EXAMPLE 8.1**

Given that the hybrid parameters for the transistor are  $h_{\rm ie}=1.5~{\rm k}\Omega$ ,  $h_{\rm fe}=150$ ,  $h_{\rm re}=1\times10^{-4}$  and  $h_{\rm oe}=20~\mu$ mhos. Draw the hybrid equivalent circuit of the transistor in all the three configurations.

#### **Solution**

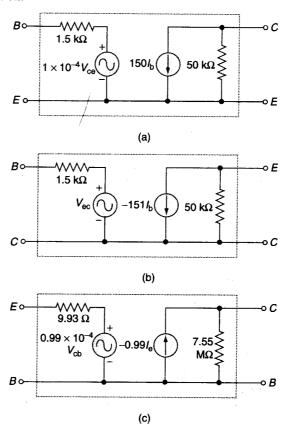

- 1. Figure 8.8(a) shows the hybrid equivalent circuit for the transistor in the common-emitter configuration.

- 2. The values of hybrid parameters in the common-collector configuration are

$$h_{c} = h_{c}$$

,  $h_{c} = 1$ ,  $h_{c} = -(1 + h_{c})$  and  $h_{c} = h_{c}$

- $h_{\rm ic} = h_{\rm ie}$ ,  $h_{\rm rc} = 1$ ,  $h_{\rm fc} = -(1 + h_{\rm fc})$  and  $h_{\rm oc} = h_{\rm oe}$ 3. Therefore,  $h_{\rm ic} = 1.5 \, {\rm k}\Omega$ ,  $h_{\rm rc} = 1$ ,  $h_{\rm fc} = -151$  and  $h_{\rm oc} = 20 \, \mu {\rm mhos}$ . 4. Figure 8.8(b) shows the hybrid equivalent circuit of the transistor in the common-collector configuration.

- 5. The values of hybrid parameters in the common-base configuration are

$$h_{ib} = \frac{h_{ic}}{1 + h_{fc}}$$

$$= (1.5 \times 10^3)/151 = 9.93 \Omega$$

$$h_{\rm rb} = \frac{h_{\rm ie}h_{\rm oe}}{1 + h_{\rm fe}} - h_{\rm re}$$

$$= [(1.5 \times 10^3 \times 20 \times 10^{-6})/151] - 1 \times 10^{-4} = 0.99 \times 10^{-4}$$

$$h_{\rm fb} = -\frac{h_{\rm fe}}{1 + h_{\rm fe}}$$

$$= -150/151 = -0.99$$

$$h_{\rm ob} = \frac{h_{\rm oe}}{1 + h_{\rm fe}}$$

$$= (20 \times 10^{-6})/151 = 0.13 \times 10^{-6}$$

**6.** Figure 8.8(c) shows the hybrid equivalent of the transistor in the common-base configuration.

Figure 8.8 | Solution to Example 8.1.

#### Graphical Determination of h-Parameters

The values of the h-parameters can be determined graphically by making use of the transistor's input and output characteristics. The parameters  $h_i$  and  $h_r$  are determined from the input characteristic curves of the transistor whereas the parameters  $h_f$  and  $h_o$  are determined from the output characteristic curves. In this section we describe the procedure for determining the h-parameters graphically for common-emitter transistor configuration. The procedure for determining the h-parameters of the common-base and common-collector configurations is similar to that for the common-emitter configuration.

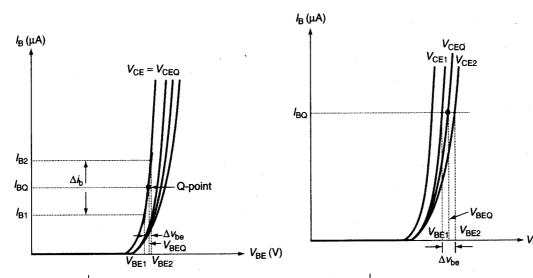

The first step in determining the h-parameters is to determine the Q-point or the operating point. Figure 8.9 shows the typical input characteristic curve for a transistor in the common-emitter configuration. As we can see from the characteristic curve, the values of the emitter-base voltage, collector-emitter voltage and the base current at the Q-point are given by  $V_{\rm BEQ}$ ,  $V_{\rm CEQ}$  and  $I_{\rm BQ}$ , respectively. The parameter  $h_{\rm ie}$  is determined by drawing a line tangent to the input characteristic curve corresponding to  $V_{\rm CEQ}$  at the Q-point. The value of the parameter  $h_{\rm ie}$  is given by the slope of this line. In other words,  $h_{\rm ie}$  is the ratio of small change in the value of emitter-base voltage to the small change in the value of base current around the operating point as shown in the figure. Therefore, the value of  $h_{\rm ie}$  is given by

$$h_{ie} = \frac{V_{BE2} - V_{BE1}}{I_{B2} - I_{B1}} \bigg|_{V_{CE} = V_{CEQ}} = \frac{\Delta v_{be}}{\Delta i_{b}} \bigg|_{V_{CE} = V_{CEQ}}$$

(8.17)

The parameter  $h_{\rm re}$  is also determined using the input characteristic curve (Figure 8.10). A horizontal line is drawn at  $I_{\rm B}$  equal to  $I_{\rm BQ}$ , that is, for the value of the base current equal to the quiescent value of the base current. The change in emitter—base voltage is determined for a small change in the value of collector—emitter voltage around the operating point. The value of  $h_{\rm re}$  is then determined by the ratio of the change in the value of emitter—base

**Figure 8.9** Determination of h-parameter  $h_{ie}$ .

**Figure 8.10** Determination of h-parameter  $h_{re}$ .

voltage to the change in the value of collector-emitter voltage for a constant value of base current. The value of  $h_{re}$ is given by

$$h_{\rm re} = \frac{V_{\rm BE2} - V_{\rm BE1}}{V_{\rm CE2} - V_{\rm CE1}} \bigg|_{I_{\rm B} = I_{\rm BQ}} = \frac{\Delta \nu_{\rm be}}{\Delta \nu_{\rm ce}} \bigg|_{I_{\rm B} = I_{\rm BQ}}$$

(8.18)

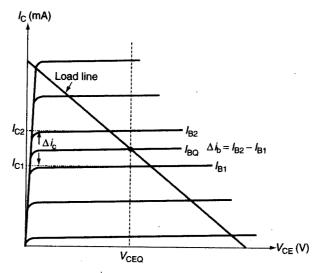

The other two parameters, that is,  $h_{\rm fe}$  and  $h_{\rm oe}$  are determined from the output characteristics. The value of parameter  $h_{\mathrm{fe}}$  is determined by drawing a vertical line corresponding to the quiescent value of collector–emitter voltage  $(V_{\text{CEQ}})$ . The value of  $h_{\text{fe}}$  is then determined by taking a small change in the base current and then determined mining the corresponding change in the collector current.  $h_{\rm fe}$  is the ratio of the change in the collector current to the change in the base current (Figure 8.11). It may be mentioned here that the accuracy of the results improves for small values of the changes. The value of  $h_{

m fe}$  is given by

$$h_{fe} = \frac{I_{C2} - I_{C1}}{I_{B2} - I_{B1}} \bigg|_{V_{CE} = V_{CEQ}} = \frac{\Delta i_{c}}{\Delta i_{b}} \bigg|_{V_{CE} = V_{CEQ}}$$

(8.19)

The value of the parameter  $b_{oe}$  is determined by drawing a tangent to the output curve corresponding to base current equal to the quiescent base current. The value of the  $b_{oe}$  parameter is then determined by taking the ratio of the change in the collector current corresponding to a small change in the collector-emitter voltage (Figure 8.12). The value of  $h_{oe}$  is given by

$$h_{\infty} = \frac{I_{C2} - I_{C1}}{V_{CE2} - V_{CE1}} \Big|_{I_{B} = I_{BQ}} = \frac{\Delta i_{c}}{\Delta v_{\infty}} \Big|_{I_{B} = I_{BQ}}$$

(8.20)

**Figure 8.11** Determination of h-parameter  $h_{\text{fe}}$

Figure 8.12 Determination of h-parameter h<sub>oe</sub>.

Table 8.2 Typical h-parameter values for silicon transistor

| Paramet        | er Common-emitter                             | Common-collector | Common-base                                 |

|----------------|-----------------------------------------------|------------------|---------------------------------------------|

| h <sub>i</sub> | 1–6.5 kΩ                                      | 1–6.5 kΩ         | 20–30 Ω                                     |

| $b_{\rm r}$    | $(1.5 \times 10^{-4}) - (2.5 \times 10^{-4})$ | 1                | $(0.1 \times 10^{-4}) - (3 \times 10^{-4})$ |

| $b_{ m f}$     | 50–250                                        | (-50) - (-250)   | -1                                          |

| $b_{\rm o}$    | 5–25 µmhos                                    | 5–25 µmhos       | 0.02-0.5 µmhos                              |

Typical h-parameter values of the NPN silicon transistor for the three amplifier configurations are given in Table 8.2.

# 8.4 Analysis of a Transistor Amplifier using Complete h-Parameter Model

Figure 8.13 shows a generalized transistor-based amplifier where the transistor is replaced by its h-parameter model. As we can see from the figure, resistor  $R_{\rm L}$  is the external load and  $V_{\rm s}$  is the input signal source. The important parameters of any amplifier are the current gain, input impedance, voltage gain and the output impedance. The expressions for these parameters will be derived in this section.

Figure 8.13 Generalized h-parameter model of a transistor-based amplifier.

1. Current gain or the current amplification  $(A_i)$ : Current gain is defined as the ratio of the current through the load resistance  $(I_L)$  to the input current  $(I_i)$ . The following equation gives the expression for the current gain:

$$A_{\rm i} = \frac{I_{\rm L}}{I_{\rm i}} \tag{8.21}$$

As the current  $I_L = -I_o$ , therefore

$$A_{\rm i} = -\frac{I_{\rm o}}{I_{\rm i}} \tag{8.22}$$

Applying Kirchhoff's current law to the output section of the circuit shown in Figure 8.13, the value of  $I_o$  is given by

$$I_{o} = h_{f}I_{i} + h_{o}V_{o} \tag{8.23}$$

The value of the output voltage  $V_o$  is given by

$$V_{o} = I_{L} R_{L} = -I_{o} R_{L} \tag{8.24}$$

Therefore, the current gain  $(A_i)$  is given by

$$A_{\rm i} = -\frac{h_{\rm f}}{1 + h_{\rm o} R_{\rm I}} \tag{8.25}$$

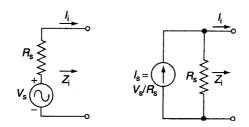

This is the current gain without taking the source resistor  $(R_s)$  into account. The overall current gain taking source resistor into account can be determined by replacing the voltage source with its Norton's equivalent as shown in Figure 8.14.

The overall current gain is determined using the following expression:

$$A_{\rm is} = -\frac{I_{\rm o}}{I_{\rm s}} \tag{8.26}$$

The above equation can be rewritten as

$$A_{is} = -\frac{I_o}{I_i} \times \frac{I_i}{I_s} = A_i \times \frac{I_i}{I_s}$$

The value of current  $I_i$  is given by

$$I_{i} = I_{s} \times \left(\frac{R_{s}}{Z_{i} + R_{s}}\right) \tag{8.27}$$

Figure 8.14 Norton's equivalent of a voltage source.

Therefore, the overall current gain  $(A_{is})$  is given by

$$A_{is} = A_{i} \times \left(\frac{R_{s}}{Z_{i} + R_{s}}\right) \tag{8.28}$$

From Eq. (8.28), it is clear that when  $R_s \to \infty$ ,  $A_{is} \to A_i$ . Therefore,  $A_i$  is the current gain for an ideal current source.

2. Input impedance  $(Z_i)$ : The input impedance  $Z_i$  is defined as the impedance seen looking into the input terminals A-A' of the amplifier. It is given by

$$Z_{i} = \frac{V_{i}}{I_{i}} \tag{8.29}$$

Applying Kirchhoff's voltage law to the input section of the amplifier we get

$$V_{i} = h_{i}I_{i} + h_{r}V_{o} (8.30)$$

Substituting the value of  $V_i$  given by Eq. (8.30) in Eq. (8.29), we get

$$Z_{i} = \frac{h_{i}I_{i} + h_{r}V_{o}}{I_{i}}$$

(8.31)

The output voltage  $V_o$  is given by

$$V_{o} = -I_{o}R_{L} = A_{i}I_{i}R_{L} \tag{8.32}$$

Substituting the value of  $V_0$  in Eq. (8.31), we get

$$Z_{i} = \frac{h_{i}I_{i} + h_{r}A_{i}I_{i}R_{L}}{I_{i}} = h_{i} + h_{r}A_{i}R_{L}$$

Substituting the value of  $A_i$  given in Eq. (8.25) in the above equation we get

$$Z_{i} = h_{i} - \frac{h_{r} h_{f} R_{L}}{1 + h_{o} R_{r}}$$

(8.33)

3. Voltage gain  $(A_v)$ : The voltage gain  $A_v$  is given by the ratio of the output voltage  $(V_o)$  to the input voltage  $(V_i)$ .

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm o}}$$

Substituting the value of  $V_0$  given in Eq. (8.32) in the above equation, we get

$$A_{\rm v} = \frac{A_{\rm i} I_{\rm i} R_{\rm L}}{V_{\rm i}} \tag{8.34}$$

Substituting the value of  $V/I_i = Z_i$ , we get

$$A_{\rm v} = \frac{A_{\rm i} R_{\rm L}}{Z_{\rm i}}$$

The voltage gain taking source resistance  $R_s$  into account  $(A_{vs})$  is given by

$$A_{vs} = \frac{V_o}{V_s} = \frac{V_o}{V_i} \times \frac{V_i}{V_s} = A_v \times \frac{V_i}{V_s}$$

(8.35)

From the equivalent input circuit of the amplifier, the voltage  $(V_i)$  is expressed in terms of the signal voltage  $(V_i)$  by

$$V_{i} = \frac{V_{s}Z_{i}}{Z_{i} + R_{s}} \tag{8.36}$$

Therefore, the expression for  $A_{vs}$  is given by

$$A_{\rm vs} = \frac{A_{\rm v}Z_{\rm i}}{Z_{\rm i} + R_{\rm c}} \tag{8.37}$$

When  $R_s \to 0$  then  $A_{vs} \to A_v$ . In other words,  $A_v$  is the voltage gain for an ideal voltage source, that is, the one with zero internal resistance.

**4.** Output admittance  $(Y_o)$ : The output admittance  $(Y_o)$  is defined as the reciprocal of the output impedance  $(Z_o)$ . The output impedance  $(Z_o)$  is determined by setting the voltage source  $(V_o)$  to zero and the load impedance  $R_L$  to infinity and by driving the output terminals from a voltage source  $(V_o)$ .  $Z_o$  is then given by the ratio of the applied voltage  $(V_o)$  to output current  $(I_o)$ .

$$Y_{o} = \frac{I_{o}}{V_{o}} \bigg|_{V_{s} = 0, R_{L} = \infty}$$

(8.38)

Substituting the value of  $I_0$  from Eq. (8.23) in Eq. (8.38), we get

$$Y_{o} = h_{f} \frac{I_{i}}{V_{o}} + h_{o}$$

(8.39)

Applying Kirchhoff's voltage law to the input section of the circuit in Figure 8.13, we get

$$V_{c} - R_{c}I_{i} - h_{i}I_{i} - h_{c}V_{0} = 0 (8.40)$$

As  $V_s = 0$ , therefore

$$R_{s}I_{i} + h_{i}I_{i} + h_{r}V_{o} = 0 (8.41)$$

Rearranging the terms in Eq. (8.41), we get

$$\frac{I_{i}}{V_{o}} = -\frac{h_{r}}{h_{i} + R_{s}} \tag{8.42}$$

Substituting the value of  $I/V_0$  given by Eq. (8.42) in Eq. (8.39), we get

$$Y_{o} = h_{o} - \frac{h_{f} h_{r}}{h_{i} + R_{s}}$$

(8.43)

In this expression, it is assumed that the load  $R_{\rm L}$  is external to the amplifier. If the effect of load resistor  $R_{\rm L}$  is included, then the total impedance is given by the parallel combination of  $Z_{\rm o}$  and  $R_{\rm L}$ .

#### **EXAMPLE 8.2**

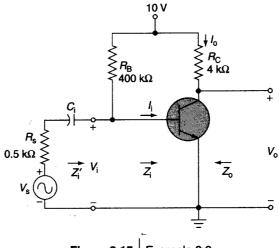

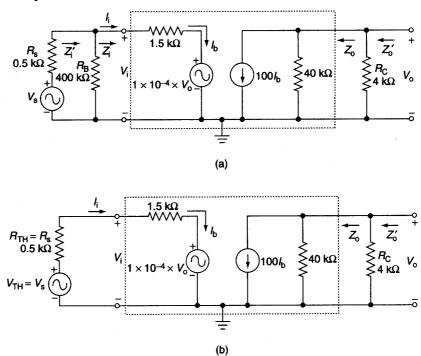

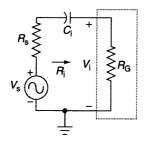

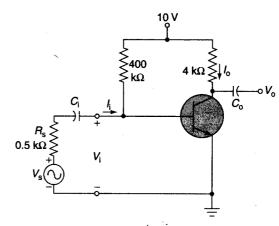

For the circuit shown in Figure 8.15, determine the input impedance, voltage gain, current gain and output impedance. The values of the h-parameters of the transistor are  $h_{\rm ic}=1.5~{\rm k}\Omega$ ,  $h_{\rm fc}=100$ ,  $h_{\rm re}=1\times10^{-4}$  and  $h_{\rm oc}=25~{\rm \mu A/V}$ .

Figure 8.15 Example 8.2.

#### Solution

The complete hybrid equivalent model for the network in Figure 8.15 is shown in Figure 8.16(a). Figure 8.16(b) shows the simplified circuit of the network shown in Figure 8.16(a) with the input section being replaced by its Thevenin's equivalent circuit.

Figure 8.16 | Solution to Example 8.2.

As the resistor  $R_{\rm B}>>R_{\rm s}$ , therefore the Thevenin's equivalent voltage  $V_{\rm TH}$  is approximately equal to the source voltage  $V_s$  and the Thevenin's equivalent resistance  $R_{\mathrm{TH}}$ is approximately equal to the resistor  $R_c$ .

2. The input impedance  $Z_i$  is equal to

$$Z_{i} = h_{ic} - \frac{h_{fc} h_{rc} R_{C}}{1 + h_{oc} R_{C}}$$

$$= 1.5 \times 10^{3} - \frac{100 \times 1 \times 10^{-4} \times 4 \times 10^{3}}{1 + 25 \times 10^{-6} \times 4 \times 10^{3}}$$

$$= 1.5 \times 10^{3} - \frac{40}{1.1}$$

$$= 1500 - 36.36 = 1.464 \text{ k}\Omega$$

3. The voltage gain  $A_{v}$  is equal to

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{-h_{fe}R_{C}}{h_{ie} + (h_{ie}h_{oe} - h_{fe}h_{re})R_{C}}$$

$$= \frac{-100 \times 4 \times 10^{3}}{1.5 \times 10^{3} + (1.5 \times 10^{3} \times 25 \times 10^{-6} - 100 \times 1 \times 10^{-4}) \times 4 \times 10^{3}}$$

$$= \frac{-4 \times 10^{5}}{1.5 \times 10^{3} + 0.0275 \times 4 \times 10^{3}}$$

$$= \frac{-4 \times 10^{5}}{1.61 \times 10^{3}} = -248.45$$

**4.** The current gain  $A_i$  is equal to

$$A_{\rm i} = -\frac{h_{\rm fc}}{1 + h_{\rm oc}R_{\rm C}}$$

$$= \frac{-100}{1 + 25 \times 10^{-6} \times 4 \times 10^{3}}$$

$$= -90.91$$

- 5. The output impedance  $Z_0'$  is parallel combination of  $Z_0$  and  $R_C$ .

- **6.**  $Z_0$  is given by

$$Z_{o} = \frac{1}{h_{oc} - [h_{fe}h_{re}/(h_{ic} + R_{s})]}$$

$$= \frac{1}{25 \times 10^{-6} - [(100 \times 1 \times 10^{-4})/(1.5 \times 10^{3} + 500)]}$$

$$= \frac{1}{25 \times 10^{-6} - 5 \times 10^{-6}} = 50 \text{ k}\Omega$$

7. The overall output impedance  $Z_o' = 50 \times 10^3 \| 4 \times 10^3 = 3.7 \times 10^3 =$

# 8.5 Analysis of Transistor Amplifier Configurations using Simplified h-Parameter Model

The simplified h-parameter model of a transistor was discussed in the Section 8.3. In this section, we will discuss the analysis of the various transistor amplifier configurations using the simplified h-parameter model.

#### Common-Emitter Configuration

The analysis for the fixed-bias configuration, voltage-divider configuration, emitter-bias configuration with unbypassed emitter resistor is discussed in the following subsections.

#### Fixed-Bias Configuration

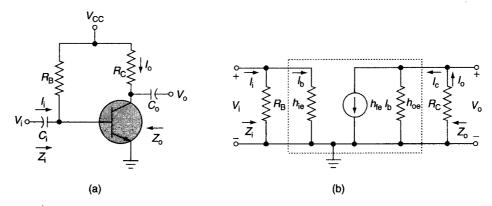

Figure 8.17(a) shows the circuit diagram of the fixed-bias configuration and Figure 8.17(b) shows the simplified h-parameter equivalent model.

The input impedance  $Z_i$  is given by a parallel combination of resistor  $R_B$  and transistor's  $h_{ie}$  parameter:

$$Z_{i} = R_{B} \left\| b_{ie} \right\| \tag{8.44}$$

The output impedance  $(Z_o)$  is given by the parallel combination of resistor  $R_C$  and the inverse of the output admittance h-parameter  $h_{oe}$ :

$$Z_{0} = R_{C} \left\| (1/h_{0c}) \right\| \tag{8.45}$$

The voltage gain  $A_{v}$  is given by

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm i}} \tag{8.46}$$

The magnitude of the output voltage  $V_0$  is given by

$$V_{0} = -I_{0}Z_{0} = -I_{0}Z_{0} \tag{8.47}$$

The collector current  $(I_c)$  is given by

$$I_{c} = h_{f_{e}} I_{h} \tag{8.48}$$

**Figure 8.17** (a) Circuit diagram of fixed-bias configuration; (b) simplified h-parameter equivalent model.

The base current  $(I_b)$  in turn is expressed in terms of the input voltage  $V_i$  as

$$I_{\rm b} = \frac{V_{\rm i}}{h_{\rm ic}} \tag{8.49}$$

Substituting the value of  $I_c$  given by Eq. (8.48) and value of  $I_b$  given by Eq. (8.49) in Eq. (8.47), we get

$$V_{o} = -h_{fe} \times \frac{V_{i}}{h_{ie}} \times Z_{o}$$

(8.50)

Substituting this value of  $V_0$  in the Eq. (8.46), the voltage gain is given by

$$A_{v} = \frac{-h_{fe} \times (V_{i}/h_{ie}) \times Z_{o}}{V_{i}} = \frac{-h_{fe} \times Z_{o}}{h_{ie}} = \frac{-h_{fe} \times [R_{C} | (1/h_{oe})]}{h_{fe}}$$

(8.51)

The current gain  $A_i$  is given by

$$A_{i} = \frac{I_{o}}{I_{i}} \tag{8.52}$$

The magnitude of  $I_0$  is given by

$$I_{o} = I_{c} = h_{fe}I_{b}$$

(8.53)

Base current  $I_b$  is expressed in terms of the input current  $I_i$  as

$$I_{\rm b} = \frac{R_{\rm B}}{R_{\rm R} + h_{\rm in}} \times I_{\rm i} \tag{8.54}$$

Therefore, the current gain  $A_i$  is given by

$$A_{i} = \frac{h_{fe}I_{b}}{I_{i}} = \frac{h_{fe}}{I_{i}} \times \frac{R_{B}}{R_{B} + h_{fe}} \times I_{i} = \frac{h_{fe} \times R_{B}}{R_{B} + h_{fe}}$$

(8.55)

Assuming  $R_{\rm B} >> h_{\rm ie}$ ,  $A_{\rm i} \cong h_{\rm fe}$ .

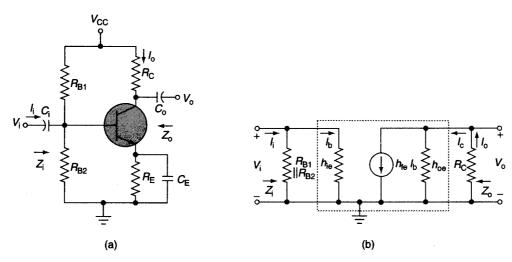

#### Voltage-Divider Configuration

Figure 8.18(a) shows the voltage-divider configuration and Figure 8.18(b) shows its h-parameter equivalent model. As we can see from the figure, the equivalent circuit is the same as in the case of fixed-bias circuit with the difference that the resistor  $R_{\rm B}$  is replaced by parallel combination of resistors  $R_{\rm B1}$  and  $R_{\rm B2}$ . The analysis for the voltage-divider configuration is done on similar lines as that for the fixed-bias configuration.

Input impedance  $Z_i$  is given by

$$Z_{i} = (R_{B1} \| R_{B2}) \| h_{ie}$$

(8.56)

The output impedance  $Z_0$  is given by the parallel combination of resistor  $R_C$  and the inverse of the output admittance h-parameter  $h_{0e}$ :

$$Z_{0} = R_{C} \| (1/h_{cc})$$

(8.57)

The voltage gain  $A_{\nu}$  is given by

$$A_{\rm v} = \frac{-h_{\rm fc} \times [R_{\rm C} \| (1/h_{\rm oc})]}{h_{\rm fc}}$$

(8.58)

Figure 8.18 (a) Circuit diagram of voltage-divider configuration; (b) simplified h-parameter model.

The current gain  $A_i$  is given by

$$A_{i} = \frac{h_{fe} \times (R_{B1} \| R_{B2})}{(R_{B1} \| R_{B2}) + h_{ie}}$$

(8.59)

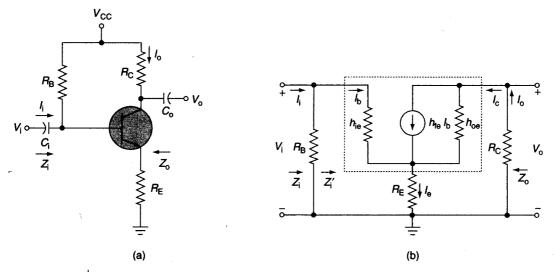

#### Emitter-Bias Configuration with Unbypassed Emitter Resistor

Figure 8.19(a) shows the circuit diagram of the emitter-bias configuration with unbypassed emitter resistor and Figure 8.19(b) shows its h-parameter model representation.

Figure 8.19 (a) Circuit diagram of emitter-bias configuration with unbypassed emitter capacitor; (b) simplified h-parameter model.

Applying Kirchhoff's voltage law to the input section we get

$$V_{i} = I_{b}h_{ic} + I_{c}R_{E} = I_{b}h_{ic} + (h_{fc} + 1)I_{b}R_{E} = [h_{ic} + (h_{fc} + 1)R_{E}]I_{b}$$

The input impedance looking into the network to the right of resistor  $R_{\rm B}$  is given by

$$Z_{i}' = \frac{V_{i}}{I_{b}} = h_{ie} + (h_{fe} + 1)R_{E}$$

(8.60)

The overall input impedance  $Z_i$  is given by parallel combination of resistor  $R_B$  and impedance  $Z_i$ :

$$Z_{i} = R_{B} \parallel Z_{i}^{\prime} \tag{8.61}$$

The voltage gain  $A_{v}$  is given by

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm i}} \tag{8.62}$$

The output voltage  $V_{o}$  is given by

$$V_{o} = -I_{o}R_{C} = -I_{c}R_{C} = -h_{fe}I_{b}R_{C}$$

(8.63)

The base current  $I_b$  is given by

$$I_{\rm b} = \frac{V_{\rm i}}{Z'} \tag{8.64}$$

Therefore, the magnitude of voltage gain  $A_{v}$  is given by

$$A_{\rm v} = -\frac{h_{\rm fe}I_{\rm b}R_{\rm C}}{V_{\rm i}} = -\frac{h_{\rm fe}R_{\rm C}}{Z_{\rm i}'} = -\frac{h_{\rm fe}R_{\rm C}}{h_{\rm ie} + (h_{\rm fe} + 1)R_{\rm E}}$$

(8.65)

The magnitude of current gain  $A_i$  is given by

$$A_{\rm i} = \frac{I_{\rm o}}{I_{\rm o}} \tag{8.66}$$

The output current  $I_{o}$  is given by

$$I_{o} = I_{c} = h_{fe}I_{b}$$

(8.67)

The base current  $I_b$  is expressed in terms of the input current  $I_i$  as

$$I_{\rm b} = \frac{R_{\rm B}}{R_{\rm n} + Z_{\rm i}'} \times I_{\rm i} \tag{8.68}$$

The value of the current gain  $A_i$  is then given by

$$A_{i} = \frac{h_{fe}I_{b}}{I_{i}} = \frac{h_{fe}R_{B}}{R_{p} + Z_{i}'} = \frac{h_{fe}R_{B}}{R_{B} + h_{ie} + (h_{fe} + 1)R_{E}}$$

(8.69)

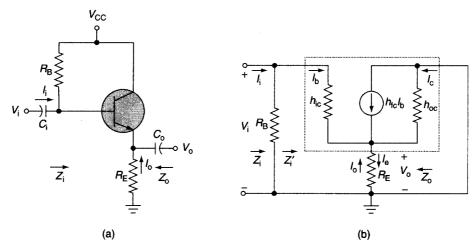

#### Emitter-Follower Configuration

Figure 8.20(a) shows the emitter-follower configuration and Figure 8.20(b) shows its h-parameter equivalent model.

The input impedance is determined in a similar manner as that for the emitter-bias configuration with unbypassed emitter resistor. The input impedance looking into the network to the right of resistor  $R_{\rm B}$  is given by

Figure 8.20 (a) Circuit diagram of emitter–follower configuration; (b) simplified h-parameter equivalent model.

$$Z_{i}' = \frac{V_{i}}{I_{b}} = h_{ic} - h_{fc}R_{E} = h_{ie} + (h_{fe} + 1)R_{E}$$

(8.70)

The overall input impedance  $Z_i$  is given by parallel combination of resistor  $R_B$  and impedance  $Z_i$ :

$$Z_{i} = R_{B} \parallel Z_{i}$$

(8.71)

The output impedance  $Z_0$  can be determined as follows.

The base current  $I_b$  is given by

$$I_{\rm b} = \frac{V_{\rm i}}{Z_{\rm i}'} \tag{8.72}$$

The emitter current  $I_e$  is then given as

$$I_{c} = -h_{fc}I_{b} = (h_{fe} + 1)I_{b} = (h_{fe} + 1) \times \frac{V_{i}}{Z'_{i}}$$

(8.73)

Substituting the value of  $Z_{\rm i}^\prime$  in the above equation we get

$$I_{c} = (h_{fe} + 1) \times \frac{V_{i}}{h_{ie} + (h_{fe} + 1)R_{E}} = \frac{V_{i}}{h_{ie}/(h_{fe} + 1) + R_{E}}$$

(8.74)

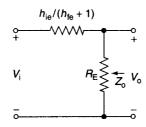

Figure 8.21 shows the network defined by Eq. (8.74).

The output impedance  $Z_0$  is defined by setting the input voltage  $V_1$  equal to zero. The output impedance  $Z_0$  is a parallel combination of resistor  $R_{\rm E}$  and impedance defined by  $h_{\rm ie}/(h_{\rm fe}+1)$ .

$$Z_{o} = R_{E} \| [h_{ie}/(h_{fe} + 1)]$$

(8.75)

From Figure 8.21, the output voltage  $V_{\rm o}$  is expressed in terms of the input voltage  $V_{\rm i}$  as

$$V_{o} = \frac{R_{E}}{R_{E} + h_{i_{c}} I(h_{E} + 1)} \times V_{i}$$

(8.76)

Figure 8.21 | Equivalent network.

The voltage gain  $A_{v}$  is then given by

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm i}} = \frac{R_{\rm E}}{R_{\rm E} + h_{\rm ic} / (h_{\rm fe} + 1)}$$

(8.77)

The current gain  $A_i$  is given by

$$A_{i} = \frac{I_{o}}{I_{:}}$$

The output current  $I_0$  is given by

$$I_{o} = -I_{e} = h_{fc}I_{b} = -(h_{fe} + 1)I_{b}$$

From Figure 8.20(b), the base current  $I_h$  is given by

$$I_{\rm b} = \frac{R_{\rm B}}{R_{\rm B} + Z_{\rm i}'} \times I_{\rm i} \tag{8.78}$$

Therefore,  $A_i$  is given by

$$A_{i} = \frac{-(h_{fe} + 1)I_{b}}{I_{i}} = \frac{-(h_{fe} + 1)R_{B}}{R_{B} + Z_{i}'}$$

(8.79)

#### Common-Base Configuration

Figure 8.22(a) shows the circuit diagram of common-base configuration and Figure 8.22(b) shows its simplified h-parameter equivalent model.

Input impedance  $Z_i$  is given by parallel combination of resistor  $R_E$  and parameter  $h_{ib}$ :

$$Z_{i} = R_{E} \| h_{ib} = R_{E} \| [h_{ie} / (h_{fe} + 1)]$$

(8.80)

The output impedance  $Z_o$  is equal to the parallel combination of collector resistor  $R_C$  and  $1/h_{ob}$ :

$$Z_{o} = R_{C} | (1/h_{ob}) \cong R_{C}$$

(8.81)

The output voltage  $V_0$  is given by

$$V_{o} = -I_{o}R_{C} = h_{fb}I_{e}R_{C}$$

(8.82)

The emitter current  $I_{\rm e}$  is expressed in terms of the input voltage  $\,V_{\rm i}$  as

$$I_{c} = -\frac{V_{i}}{h_{ib}} \tag{8.83}$$

**Figure 8.22** (a) Circuit diagram of common-base configuration; (b) simplified h-parameter equivalent model.

Therefore, voltage gain  $A_v$  is given by

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{+h_{fb}I_{e}R_{C}}{-h_{ib}I_{e}} = -\frac{h_{fb}R_{C}}{h_{ib}} = \frac{h_{fe}R_{C}}{h_{ie}}$$

(8.84)

The current gain  $A_i$  is given by

$$A_{\rm i} = \frac{I_{\rm o}}{I_{\rm i}} = \frac{-h_{\rm fb}I_{\rm e}}{I_{\rm i}} \tag{8.85}$$

The emitter current  $I_{\rm e}$  is expressed in terms of the input current  $I_{\rm i}$  by

$$I_{\rm c} = \frac{-R_{\rm E}}{R_{\rm E} + h_{\rm ib}} \times I_{\rm i} \tag{8.86}$$

Therefore, current gain is given by

$$A_{i} = \frac{h_{fb}R_{E}}{R_{E} + h_{ib}} = \frac{h_{fb}R_{E}}{R_{E} + h_{ic}/(1 + h_{fc})} \cong h_{fb}$$

(8.87)

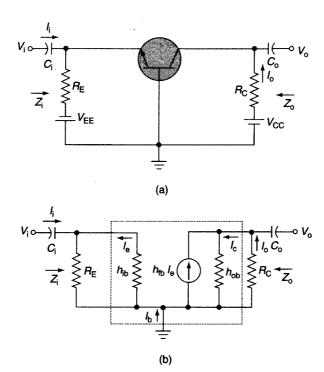

# **EXAMPLE 8.3** Determine the following parameters for the amplifier shown in Figure 8.23. Given that the h-parameters of the transistor are $h_{\rm ic} = 1 \ k\Omega$ , $h_{\rm fe} = 100$ , $h_{\rm oe} = 40 \times 10^{-6}$ mhos. (a) $Z_{\rm i}$ ; (b) $Z_{\rm o}$ ; (c) $A_{\rm v}$ ; (d) $A_{\rm i}$

Figure 8.23 Example 8.3.

#### **Solution**

1. The AC equivalent circuit for the amplifier in Figure 8.23 is shown in Figure 8.24.

Figure 8.24 | Solution to Example 8.3.

2. Input impedance

$$Z_i = R_{FI} \| b_{ie}$$

$$= 100 \times 10^3 \| 1 \times 10^3$$

$$= 0.99 \text{ k}\Omega$$

3. Output impedance  $(Z_0)$  is given by

$$Z_{o} = R_{F2} \| R_{C} \| (1/h_{oc})$$

$$= 50 \times 10^{3} \| 2 \times 10^{3} \| 25 \times 10^{3}$$

$$= 1.79 \times 10^{3} \Omega$$

$$= 1.79 \text{ k}\Omega$$

**4.** Voltage gain  $A_v$  is given by

$$A_{v} = \frac{-h_{fe} \times [R_{F2} || R_{C} || (1/h_{oe})]}{h_{fe}}$$

$$= \frac{-100 \times 1.79 \times 10^{3}}{1 \times 10^{3}}$$

$$= -179$$

5. The current gain

$$A_i$$

is given by

$$A_i = \frac{h_{fe} R_{F1} [R_{F2} || (1/h_{oe})]}{(R_{F1} + h_{ie}) [R_{F2} || (1/h_{oe}) + R_C]}$$

$$= \frac{100 \times 100 \times 10^3 \times (50 \times 10^3 || 25 \times 10^3)}{(100 \times 10^3 + 1 \times 10^3) \times (50 \times 10^3 || 25 \times 10^3 + 2 \times 10^3)}$$

$$= \frac{10^7 \times 16.67 \times 10^3}{101 \times 10^3 \times 18.67 \times 10^3} = 88.4$$

# 8.6 Small Signal Analysis of FET Amplifiers

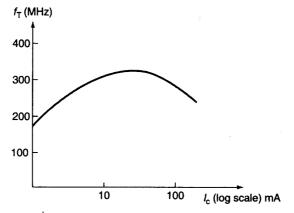

The linear small signal model for FETs can be obtained on similar lines as that for BJTs. The expression for the drain current is given by

$$I_{\rm d} = V_{\rm gs} \frac{\partial i_{\rm d}}{\partial \nu_{\rm gs}} \bigg|_{V_{\rm DS} = {\rm const.}} + V_{\rm ds} \frac{\partial i_{\rm d}}{\partial \nu_{\rm ds}} \bigg|_{V_{\rm GS} = {\rm const.}}$$

(8.88)

The parameter  $g_m$  is defined as the transconductance or the mutual conductance and is given by

$$g_{\rm m} = \frac{\partial i_{\rm d}}{\partial v_{\rm gs}} \bigg|_{V_{\rm ps} = \text{const.}}$$

(8.89)

It is also designated as  $y_{fs}$  or  $g_{fs}$  and is also referred to as forward transadmittance. The second important parameter used to define the operation of FETs is the drain resistance designated as r<sub>d</sub>. It is defined by Eq. (8.90). The reciprocal of drain resistance  $r_d$  is referred to as the drain conductance (designated as  $g_d$ ). It is also known as output conductance and is also denoted as  $y_{os}$ .

$$r_{\rm d} = \frac{\partial v_{\rm ds}}{\partial i_{\rm d}} \bigg|_{V_{\rm GS} = \text{const.}}$$

(8.90)

Substituting the values of  $g_{\rm m}$  given by Eq. (8.89) and  $r_{\rm d}$  given by Eq. (8.90) in Eq. (8.88) we get

$$I_{\rm d} = g_{\rm m} V_{\rm gs} + \frac{1}{r_{\rm a}} V_{\rm ds} \tag{8.91}$$

The amplification factor m of an FET is defined as

$$\mu = \frac{\partial v_{ds}}{\partial v_{gs}} \bigg|_{I_{c} = \text{const.}}$$

(8.92)

The parameters  $g_m$ ,  $r_d$  and m are related by the following equation:

$$\mu = r_{\rm d} g_{\rm m} \tag{8.93}$$

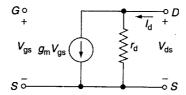

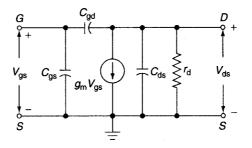

The low-frequency model of an FET is defined by Eq. (8.91) and is shown in Figure 8.25. As we can see from the figure, it has a Norton's equivalent output circuit with a voltage-dependent current source whose current output is proportional to the gate-source voltage  $(V_{gs})$ . Also, the input impedance between the gate and the source

Figure 8.25 | Low-frequency model of an FET.

terminals is infinite because it is assumed that there is no current flowing through the reverse-biased gate terminal. The above equations and the model in Figure 8.25 are applicable for both JFETs as well as MOSFETs.

When we compare this model of the FET with that of the BJT, we find that there a few major differences. First, the value of the current generated by the output current source in the case of an FET depends on the input voltage whereas in the case of a BJT it depends upon the input current. Second, in the case of an FET, there is no feedback from the output to the input whereas in the case of a BJT there is feedback between the output and the input sections through parameter  $h_{\rm re}$ . Lastly, the input impedance of an FET is much larger than that of a BJT. In nutshell, FET is more closer to being an ideal amplifier than a BJT at low frequencies.

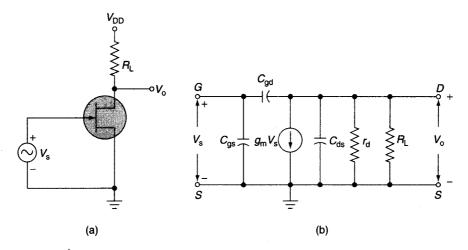

#### Common-Source FET Amplifier

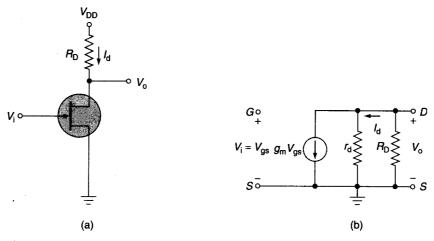

The common-source FET amplifier is shown in Figure 8.26(a). Replacing the FET by its low-frequency small signal model, the equivalent circuit of Figure 8.26(b) is obtained.

Applying Kirchhoff's voltage law to the output section we get

$$I_{\rm d}R_{\rm D} + (I_{\rm d} - g_{\rm m}V_{\rm gs})r_{\rm d} = 0 {(8.94)}$$

The voltage between the gate and the source terminals  $(V_{\rm gs})$  is equal to the input voltage  $V_{\rm i}$ . Rearranging the terms in Eq. (8.94) and substituting  $V_{\rm gs} = V_{\rm i}$ , we get

$$I_{\rm d} = \frac{g_{\rm m} r_{\rm d} V_{\rm i}}{r_{\rm d} + R_{\rm D}} = \frac{\mu V_{\rm i}}{r_{\rm d} + R_{\rm D}}$$

(8.95)

Figure 8.26 (a) Common-source FET amplifier; (b) low-frequency small signal equivalent model of the amplifier in (a).

The output voltage  $V_0$  is given by

$$V_{o} = -I_{d}R_{D} = -\frac{\mu R_{D}V_{i}}{r_{d} + R_{D}}$$

(8.96)

Therefore, the voltage gain  $A_{\nu}$  is given by

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm i}} = -\frac{\mu R_{\rm D}}{r_{\rm d} + R_{\rm D}}$$

(8.97)

For the common-source amplifier with an unbypassed source resistor  $(R_S)$ , the analysis can be carried out on similar lines and the voltage gain is given by

$$A_{\rm v} = -\frac{\mu R_{\rm D}}{r_{\rm d} + R_{\rm D} + (\mu + 1)R_{\rm S}} \tag{8.98}$$

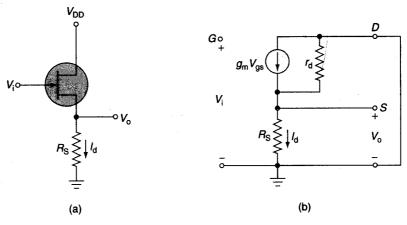

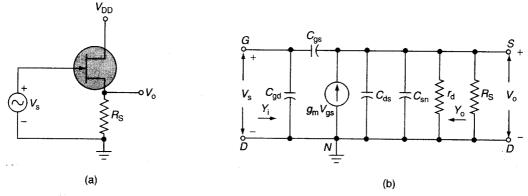

#### Common-Drain FET Amplifier

The common-drain FET amplifier is shown in Figure 8.27(a). Replacing the FET by its low-frequency small signal model, the equivalent circuit of Figure 8.27(b) is obtained. The analysis is carried on similar lines to that of the common-source FET amplifier.

Applying Kirchhoff's voltage law to the output section we get

$$I_{\rm d}R_{\rm S} + (I_{\rm d} - g_{\rm m}V_{\rm gs})r_{\rm d} = 0 \tag{8.99}$$

The gate-source voltage is expressed as

$$V_{gs} = V_{i} - I_{d} R_{S} (8.100)$$

Combining Eqs. (8.99) and (8.100) we get

$$I_{\rm d} = \frac{g_{\rm m} r_{\rm d} V_{\rm i}}{r_{\rm d} + R_{\rm S} + g_{\rm m} r_{\rm d} R_{\rm S}} = \frac{\mu V_{\rm i}}{r_{\rm d} + (\mu + 1) R_{\rm S}}$$

(8.101)

The output voltage  $V_0$  is given by

$$V_{o} = I_{d}R_{S} = \frac{\mu R_{S}V_{i}}{r_{d} + (\mu + 1)R_{S}}$$

(8.102)

Figure 8.27 (a) Common-drain amplifier; (b) low-frequency small signal equivalent model of the amplifier in part (a).

Therefore, the voltage gain  $A_{\nu}$  is given by

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm i}} = \frac{\mu R_{\rm S}}{r_{\rm d} + (\mu + 1)R_{\rm S}}$$

(8.103)

For the common-drain amplifier with an unbypassed drain resistor ( $R_{\mathrm{D}}$ ), the analysis can be carried out on similar lines and the voltage gain is given by

$$A_{\rm v} = \frac{\mu R_{\rm S}}{r_{\rm d} + R_{\rm D} + (\mu + 1)R_{\rm S}}$$

(8.104)

As the value of  $\mu$  is very large, therefore the term  $(\mu+1)R_{\rm S}>>(r_{\rm d}+R_{\rm D})$ . Therefore, Eq. (8.104) can by approximated as

$$A_{\rm v} \cong \frac{\mu R_{\rm S}}{(\mu + 1)R_{\rm S}} \cong \frac{\mu}{\mu + 1} \cong 1$$

(8.105)

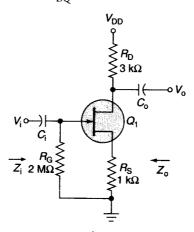

#### **EXAMPLE 8.4**

For the self-bias JFET amplifier shown in Figure 8.28, determine the value of (a)  $Z_i$ , (b)  $Z_{\rm o}$  and (c)  $A_{\rm v}$ . Given that  $I_{\rm DSS}=10$  mA,  $V_{\rm p}=-5$  V and  $r_{\rm d}=50$  k $\Omega$ . The quiescent operating point is  $V_{\rm GSQ}=-2.5$  V and  $I_{\rm DQ}=2.5$  mA.

Figure 8.28 Example 8.4.

#### Solution

- 1. Figure 8.29 shows the equivalent circuit for the amplifier in Figure 8.28.

- 2. The input impedance  $(Z_i)$  is given by  $Z_i = R_G$ . Therefore,  $Z_i = 2 \text{ M}\Omega$ .

- 3. The output impedance can be calculated as

$$Z_{o} = \frac{V_{o}}{I} \Big|_{V_{i} = 0}$$

- 4. For V<sub>i</sub> = 0, the output voltage V<sub>o</sub> is defined by V<sub>o</sub> = -I<sub>d</sub>R<sub>D</sub> and the gate-source voltage (V<sub>gs</sub>) is defined by V<sub>gs</sub> = -I<sub>d</sub>R<sub>S</sub>.

5. For V<sub>i</sub> = 0, the current through resistor r<sub>d</sub> is equal to

$$I' = \frac{V_{\rm rd}}{r_{\rm d}} = \frac{V_{\rm o} + V_{\rm gs}}{r_{\rm d}} = \frac{-I_{\rm d}(R_{\rm D} + R_{\rm S})}{r_{\rm d}}$$

Figure 8.29 | Solution to Example 8.4.

- **6.** Applying KCL at the drain node (D),  $I_d + I_o = I' + g_m V_{gs}$ .

- 7. Therefore,

$$I_{o} = -I_{d} \left( 1 + g_{m} R_{S} + \frac{R_{D} + R_{S}}{r_{d}} \right)$$

**8.** Therefore,  $Z_0$  is given by

$$Z_{o} = \frac{R_{D}}{1 + g_{m}R_{S} + [(R_{D} + R_{S})/r_{d}]}$$

**9.** The value of  $g_m$  is given by

$$g_{\rm m} = g_{\rm mo} \left( 1 - \frac{V_{\rm GSQ}}{V_{\rm p}} \right)$$

10.

$$g_{\text{mo}} = \frac{2I_{\text{DSS}}}{|V_{\text{p}}|}$$

$$= \frac{2 \times 10 \times 10^{-3}}{5}$$

- 11. Therefore,  $g_{\rm m} = 4 \times 10^{-3} \left[ 1 (-2.5)/(-5) \right] = 2 \text{ mS}$

- 12. Output impedance  $Z_0$  is given by

$$Z_o = 3 \times 10^3/[1 + 2 \times 10^{-3} \times 1 \times 10^3 + (3 \times 10^3 + 1 \times 10^3)/(50 \times 10^3)]$$

= (3 × 10<sup>3</sup>)/(3 + 0.08) = 0.97 kΩ

13. The value of voltage gain  $A_{\rm v}$  can be calculated as follows:

Applying KVL to the input section we get  $V_{es} = V_i - I_d R_S$

14. Applying KCL to the drain node (D) we get

$$I_{\rm d} = g_{\rm m} V_{\rm gs} + \frac{V_{\rm o} - V_{\rm RS}}{r_{\rm d}}$$

- **15.** Output voltage  $V_0$  is equal to  $V_0 = -I_d R_D$ .

16. Therefore,

$$I_{\rm d}$$

is given by

$$I_{\rm d} = \frac{g_{\rm m}V_{\rm i}}{1+g_{\rm m}R_{\rm S}+[(R_{\rm D}+R_{\rm S})/r_{\rm d}]}$$

17. Voltage gain

$$A_{v}$$

is equal to

$$A_{v} = \frac{V_{o}}{V_{i}} = -\frac{g_{m}R_{D}}{1 + g_{m}R_{S} + [(R_{D} + R_{S})/r_{d}]}$$

$$= \frac{-2 \times 10^{-3} \times 3 \times 10^{3}}{1 + 2 \times 10^{-3} \times 1 \times 10^{3} + [(3 \times 10^{3} + 1 \times 10^{3})/(50 \times 10^{3})]}$$

$$= -1.95$$

## 8.7 Cascading Amplifiers

any times, the gain of a single-amplifier stage is not sufficient for the intended application or the f 1 input or the output impedance of the amplifier is not of the correct magnitude for the given application. In such cases, two or more amplifier stages are cascaded, that is, the output of a given stage is connected to the input of the next amplifier stage. A cascade connection of amplifiers is a series connection where the output of one stage is applied to the input of the next stage. As an example, the common-emitter amplifier is used for cascading to provide power gain, common-collector amplifier may be used as the last stage to drive a low-resistance load as it has low output resistance or it may be used as first stage of the amplifier by virtue of its high input impedance.

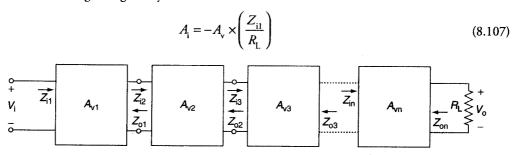

Figure 8.30 shows a generalized cascaded amplifier connection. The total gain is the product of the gains of the individual amplifier stages under loaded conditions. The overall gain  $(A_{\nu})$  is therefore given by

$$A_{\mathbf{v}} = A_{\mathbf{v}1} \times A_{\mathbf{v}2} \times A_{\mathbf{v}3} \times \dots \times A_{\mathbf{v}n} \tag{8.106}$$

where  $A_{\rm v}$  is the overall voltage gain;  $A_{\rm v1}$  is the voltage gain of stage 1 with the input impedance of stage 2 acting on it;  $A_{v2}$  is the voltage gain of stage 2 with the input impedance of stage 3 acting on it and its source impedance is the output impedance of stage 1;  $A_{v3}$  is the voltage gain of stage 3 with the input impedance of stage 4 acting on it and its source impedance is the output impedance of stage 2;  $A_{\rm vn}$  is the voltage gain of stage n with the load impedance acting on it and its source impedance is the output impedance of stage (n-1).

The overall current gain is given by

Figure 8.30 | Generalized cascaded amplifier connection.

where  $A_i$  is the overall current gain;  $A_v$  is the overall voltage gain;  $Z_{i1}$  is the input impedance of the stage 1;  $R_1$  is the load resistance.

It may be mentioned here that the DC bias conditions for the cascaded amplifier stages can be determined on similar lines as that discussed in Chapter 4 for BJT amplifiers and in Chapter 5 for FET amplifiers.

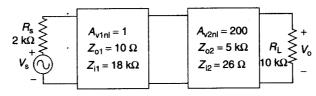

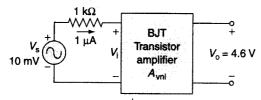

#### **EXAMPLE 8.5**

Figure 8.31 shows a two-stage CC-CB amplifier. The values of input and output impedances and the voltage gains for each stage are shown in the figure. All the values are for no-load conditions. However, the input impedance and the output impedance of the first stage are under loaded conditions. Determine

- (a) The loaded voltage gain for each stage.

- (b) The overall voltage gain of the amplifier.

- (c) The total system voltage and current gain.

Figure 8.31 | Example 8.5.

#### Solution

1. The loaded voltage gain of the second-stage, that is, the CB amplifier is given by

$$A_{v2} = A_{v2nl} \times [R_L / (R_L + Z_{o2})]$$

= 200 \times [(10 \times 10^3) / (10 \times 10^3 + 5 \times 10^3)]

= 133.33

2. The loaded voltage gain of the first stage, that is, the CC amplifier is given by

$$A_{v1} = A_{v1ol} \times [Z_{i2}/(Z_{i2} + Z_{o1})] = 1 \times [26/(26 + 10)] = 26/36 = 0.722$$

- 3. The overall voltage gain of the amplifier =  $A_{v1} \times A_{v2} = 0.722 \times 133.33 = 96.26$ .

- 4. The value of total system voltage gain

$$A_{vs} = A_{v} \times [Z_{i1}/(Z_{i1} + R_{s})] = 96.26 \times [(18 \times 10^{3})/(18 \times 10^{3} + 2 \times 10^{3})]$$

$$= -86.63$$

5. The value of the total system current gain

$$A_{\rm is} = -(A_{\rm vs} \times Z_{\rm i1})/R_{\rm L} = -(86.63 \times 18 \times 10^3)/(10 \times 10^3) = -155.93$$

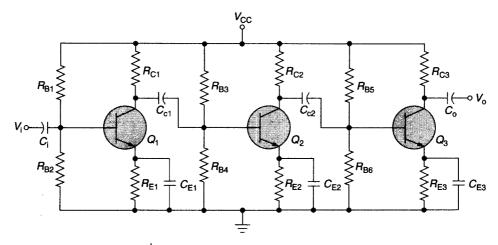

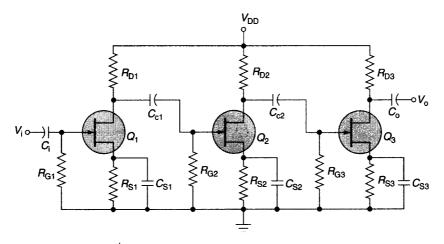

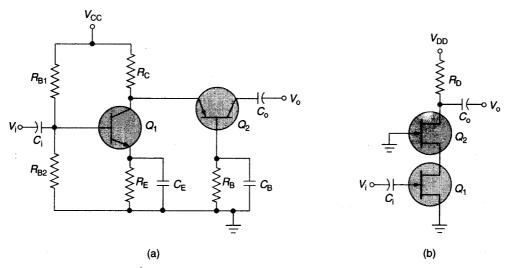

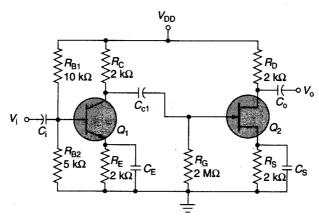

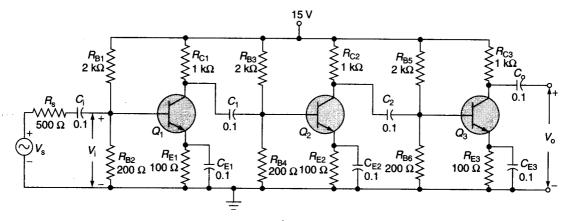

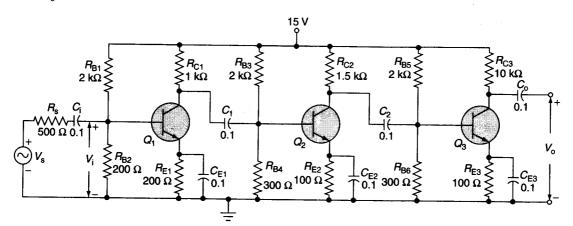

**BJT Cascade Amplifier**

Figure 8.32 shows a cascaded three-stage RC-coupled BJT amplifier. Let the h-parameters of the transistor  $Q_1$  be  $h_{\text{ie}1}$ ,  $h_{\text{fe}1}$ ,  $h_{\text{re}1}$  and  $h_{\text{oe}1}$ ; of transistor  $Q_2$  be  $h_{\text{ie}2}$ ,  $h_{\text{fe}2}$ ,  $h_{\text{fe}2}$ , and  $h_{\text{oe}2}$  and that of transistor  $Q_3$  be  $h_{\text{ie}3}$ ,  $h_{\text{fe}3}$ ,  $h_{\text{re}3}$  and  $h_{\text{oe}3}$ .

Figure 8.32 Cascaded three-stage RC-coupled BJT amplifier.

The voltage gain of the third stage is given by

$$A_{v3} = \frac{-h_{fe3} \times [R_{C3} \| (1/h_{oe3})]}{h_{fe3}}$$

(8.108)

Assuming  $1/h_{oe} >> R_{C3}$ , the equation can be simplified as

$$A_{v3} = \frac{-h_{fe3} \times R_{C3}}{h_{fe3}} \tag{8.109}$$

Similarly, the gain for the second stage  $A_{v2}$ , assuming  $1/h_{oe2} >> R_{B5} \|R_{B6}\| R_{C2} \|h_{ie3}$  is given by

$$A_{v2} = \frac{-h_{fe2} \times (R_{B5} \| R_{B6} \| R_{C2} \| h_{fe3})}{h_{fe2}}$$

(8.110)

The gain for the first stage  $A_{\rm v1}$ , assuming  $1/h_{\rm oc1}>>R_{\rm B3}\left\|R_{\rm B4}\left\|R_{\rm C1}\right\|h_{\rm ic2}$  is given by

$$A_{v1} = \frac{-h_{fe1} \times (R_{B3} \| R_{B4} \| h_{fe1})}{h_{fe1}}$$

(8.111)

The overall voltage gain  $A_{v}$  is given by the product of the voltage gains of the three stages:

$$A_{v} = A_{v1} \times A_{v2} \times A_{v3} \tag{8.112}$$

The overall input impedance of the amplifier is the same as the input impedance of stage 1 and is given by

$$Z_{i} = R_{B1} \| R_{B2} \| b_{ie1}$$

(8.113)

The output impedance of the amplifier is equal to the output impedance of the last stage and is given by

$$Z_{o} = R_{C3} \left\| (1/h_{oc3}) \right\| \tag{8.114}$$

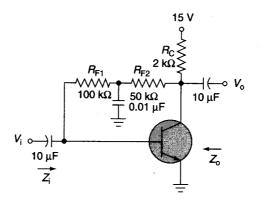

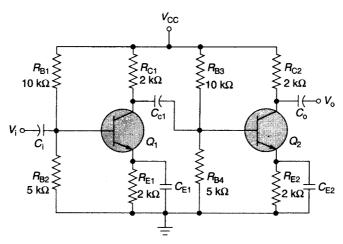

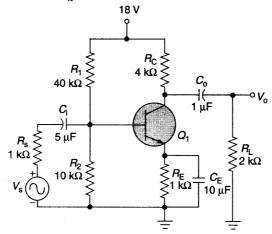

#### **EXAMPLE 8.6**

Figure 8.33 shows a two-stage BJT cascaded amplifier. Calculate the voltage gain, input and output impedance of the amplifier, given that  $h_{ie}$  and  $h_{fe}$  parameters of both the transistors are 1 k $\Omega$  and 100, respectively. Assume that the effect of  $h_{oe}$  is negligible.

Figure 8.33 Example 8.6.

#### Solution

1. Voltage gain of the second stage is given by

$$A_{v2} = \frac{-h_{fe2} \times R_{C2}}{h_{ie2}}$$

$$= \frac{-100 \times 2 \times 10^3}{1 \times 10^3} = -200$$

2. Voltage gain of the first stage is given by

$$A_{v1} = \frac{-h_{fe1} \times (R_{B3} || R_{B4} || R_{C1} || h_{ie2})}{h_{ie1}}$$

$$= \frac{-100 \times (10 \times 10^3 || 5 \times 10^3 || 2 \times 10^3 || 1 \times 10^3)}{1 \times 10^3}$$

$$= \frac{-100 \times 555.56}{1 \times 10^3} = -55.556$$

3. Overall voltage gain is given by  $A = A \times A = -200 \times -55.55$

- 3. Overall voltage gain is given by  $A_v = A_{v1} \times A_{v2} = -200 \times -55.556 = 11111.2$ .

- **4.** The input impedance of the amplifier  $Z_i$  is given by

$$Z_{i} = R_{B1} \| R_{B2} \| b_{ie1}$$

=  $10 \times 10^{3} \| 5 \times 10^{3} \| 1 \times 10^{3} = 769.05 \Omega$

5. The output impedance of the amplifier is given by  $Z_o = R_{\rm C2} \| (1/h_{\rm oc2})$ . As the effect of  $h_{\rm oc}$  is negligible, therefore  $Z_o = R_{\rm c2} = 2 \ {\rm k}\Omega$ .

Figure 8.34 | Cascaded three-stage RC-coupled JFET amplifier.

#### FET Cascade Amplifier

Figure 8.34 shows a cascaded three-stage RC-coupled JFET amplifier. The gains of the first, second and third stages are given respectively by the following three equations:

$$A_{\rm vl} = -g_{\rm ml} R_{\rm Dl} \tag{8.115}$$

$$A_{v2} = -g_{m2}R_{D2} \tag{8.116}$$

$$A_{v3} = -g_{m3}R_{D3} \tag{8.117}$$

where  $R_{\rm D1}$ ,  $R_{\rm D2}$  and  $R_{\rm D3}$  are the drain resistors for stage-1, stage-2 and stage-3 amplifiers respectively;  $g_{\rm m1}$ ,  $g_{\rm m2}$  and  $g_{\rm m3}$  are the transconductance values for the stage-1, stage-2 and stage-3 amplifiers, respectively. The overall gain  $A_{\rm v}$  is given by

$$A_{v} = A_{v1} \times A_{v2} \times A_{v3} \tag{8.118}$$

The input impedance  $Z_i$  of the cascaded amplifier is the same as the input impedance of the stage 1:

$$Z_{\rm i} = R_{\rm G1}$$

(8.119)

The output impedance  $Z_0$  is given by the output impedance of the last stage:

$$Z_0 = R_{D3}$$

(8.120)

A combination of FET and BJT stages can also be used to provide both high value of voltage gain as well as high value of input impedance.

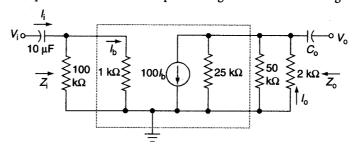

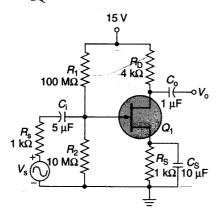

#### **EXAMPLE 8.7**

Figure 8.35 shows a two-stage cascaded amplifier with the first stage as a common-source JFET amplifier and the second stage as a common-emitter BJT amplifier. Calculate the voltage gain, input and output impedances of the amplifier. Given that  $h_{\rm ie}$  and  $h_{\rm fe}$  parameters of the transistor are 1 k $\Omega$  and 100, respectively. Assume that the effect of  $h_{\rm oe}$  is negligible. The transconductance  $g_{\rm m}$  of the JFET is 2.6 mS.

Figure 8.35 Example 8.7.

#### Solution

1. Voltage gain of the second stage is given by

$$A_{v2} = \frac{-h_{fe} \times R_{C}}{h_{ie}}$$

$$= \frac{-100 \times 2 \times 10^{3}}{1 \times 10^{3}} = -200$$

2. Voltage gain of the first stage is given by

$$A_{v1} = -g_{m} (R_{D} || R_{B1} || R_{B2} || b_{ie})$$

$$= -2.6 \times 10^{-3} \times (2 \times 10^{3} || 10 \times 10^{3} || 5 \times 10^{3} || 1 \times 10^{3})$$

$$= -2.6 \times 10^{-3} \times 555.56 = -1.45$$

- 3. Overall voltage gain is given by  $A_v = A_{v1} \times A_{v2} = -200 \times -1.45 = 290$ .

- 4. The input impedance of the amplifier  $Z_i$  is given by  $Z_i = R_G$ . Therefore,  $Z_i = 3 \text{ M}\Omega$ .

- 5. The output impedance of the amplifier is given by  $Z_o = R_C \| (1/b_{oe})$ . As the effect of  $b_{oe}$  is negligible, therefore  $Z_o = R_C = 2 \text{ k}\Omega$ .

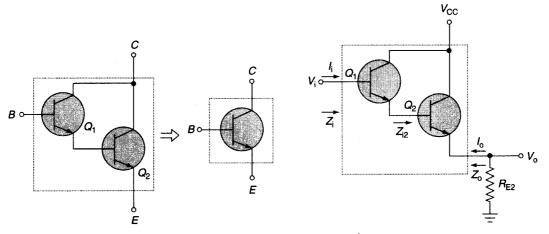

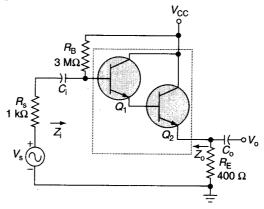

# 8.8 Darlington Amplifiers

Darlington transistors refer to the connection of two BJTs wherein their collector terminals are tied together and the emitter terminal of one of the transistors is connected to the base terminal of the other transistor. In other words, the Darlington connection can be considered as two cascaded emitter-followers, with the first stage having an infinite emitter resistance. The composite transistor acts as a single unit (Figure 8.36) with a current gain approximately equal to the product of the current gains of the individual transistors. If the individual transistors have current gains of  $\beta_1$  and  $\beta_2$ , then the Darlington connection provides an approximate current gain of  $\beta_D$  given by

$$\beta_{\rm D} = \beta_1 \times \beta_2 \tag{8.121}$$

Figure 8.36 Darlington transistor.

Figure 8.37 | Circuit using a Darlington transistor.

It offers other advantages like increased value of input impedance and reduced value of output impedance. The values of these parameters are derived in the subsequent paragraphs. Figure 8.37 shows a circuit configuration employing a Darlington pair. The biasing network for  $Q_1$  has not been included for simplicity of analysis. The current gain for the second transistor  $Q_2$  is given by

$$A_{12} = \frac{I_o}{I_{b2}} = \frac{1 + h_{fe2}}{1 + h_{oe2}R_{E2}} \cong 1 + h_{fe2}$$

(8.122)

The input resistance of the second stage is given by

$$Z_{i2} = h_{ie2} + (1 + h_{fe2})R_{E2} \cong (1 + h_{fe2})R_{E2}$$

(8.123)

$Z_{i2}$  is the effective load resistance for the first-stage  $Q_1$  and the current gain for the first stage  $(A_{i1})$  is given by

$$A_{i1} = \frac{I_{e1}}{I_i} = \frac{I_{b2}}{I_i} = \frac{1 + h_{fe1}}{1 + h_{oe1} Z_{i2}}$$

$$\approx \frac{1 + h_{fe1}}{1 + h_{oe1} (1 + h_{fe2}) R_{E2}}$$

$$\approx \frac{1 + h_{fe1}}{1 + h_{oe1} h_{fe2} R_{E2}}$$

(8.124)

The overall current gain  $(A_i)$  is given by

$$A_{i} = \frac{I_{o}}{I_{i}} = \frac{I_{o}}{I_{b2}} \times \frac{I_{b2}}{I_{i}} = A_{i2} \times A_{i1} \cong (1 + h_{fe2}) \left( \frac{1 + h_{fe1}}{1 + h_{oe1}h_{fe2}R_{E2}} \right)$$

(8.125)

Assuming that the h-parameters for both the transistors are equal, that is,  $h_{\text{fe}1} = h_{\text{fe}2} = h_{\text{fe}}$  and  $h_{\text{oe}1} = h_{\text{oe}2} = h_{\text{oe}}$ , the above equation can be rewritten as

$$A_{i} \cong \left(\frac{(1 + h_{fe})^{2}}{1 + h_{oe}h_{fe}R_{E2}}\right)$$

(8.126)

The overall voltage gain  $(A_v)$  is less than unity, because it consists of two emitter-followers in cascade, each offering value of voltage gain slightly less than unity.

$$A_{\rm v} = \frac{V_{\rm o}}{V_{\rm i}} \cong \left(1 - \frac{h_{\rm ic}}{Z_{\rm i2}}\right)$$

(8.127)

The overall input impedance  $(Z_i)$  is given by

$$Z_{i} = \frac{A_{i}R_{E2}}{A_{i}} \cong A_{i}R_{E2} \cong \frac{(1 + h_{fe})^{2}R_{E2}}{1 + h_{i} \cdot h_{f} \cdot R_{E2}}$$

(8.128)

The output impedance  $(Z_0)$  is given by

$$Z_{o} \cong \frac{R_{s} + h_{ie}}{(1 + h_{fe})^{2}} + \frac{h_{ie}}{1 + h_{fe}}$$

(8.129)

where  $R_s$  is the value of the source resistance.

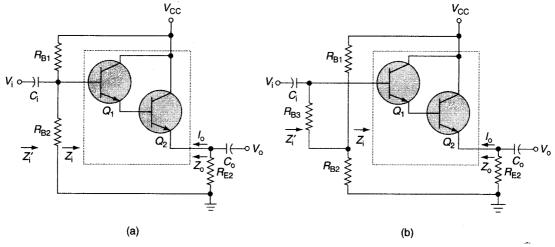

In deriving the above equations, we have omitted the biasing network for transistor  $Q_1$  to simplify the analysis. The biasing network mainly affects the input impedance of the amplifier. Figure 8.38(a) shows the biasing arrangement. Let us now consider the effect of the biasing network of transistor  $Q_1$  on the input impedance of the network.

The overall input impedance  $(Z_i)$  is given by

$$Z_i' = Z_i ||R \tag{8.130}$$

where  $R = R_{\rm B1} \| R_{\rm B2}$ . The value of R (i.e., parallel combination of  $R_{\rm B1}$  and  $R_{\rm B2}$ ) is much less than the value of  $Z_{\rm i}$ . Therefore, the overall input impedance ( $Z_{\rm i}'$ ) is appreciably smaller than  $Z_{\rm i}$ . This nullifies one of the major advantages offered by a Darlington amplifier of high input impedance.

This can be partially overcome by adding a resistor  $R_{\rm B3}$  as shown in Figure 8.38(b). The new value of R is now

$$R = R_{\rm B1} \left\| R_{\rm B2} + R_{\rm B3} \right\| \tag{8.131}$$

The value of R is still less than  $Z_i$ . The value of R can be substantially improved if we add a capacitor  $C_B$  in addition to resistor  $R_{B3}$  [Figure 8.38(c)]. The reactance of the capacitor is negligible at low frequencies at which the amplifier is to be used. Hence, the capacitor  $(C_B)$  directly couples the output voltage  $V_o$  to the lower side of resistor  $R_{B3}$ . The other end of the resistor  $R_{B3}$  is connected to the input voltage  $V_i$ . As the

(a) Darlington amplifier with input bias circuit; (b) Darlington amplifier with modified input bias circuit; (c) bootstrapping in Darlington amplifier.

Figure 8.38 | Continued.

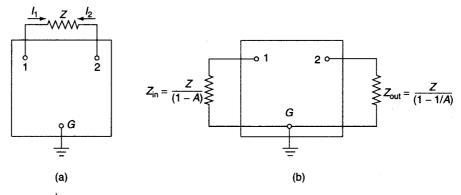

voltage gain of the amplifier is nearly unity, the input voltage  $V_i$  is approximately equal to the output voltage  $V_o$ . Therefore, there is very small AC voltage drop across the resistor  $R_{\rm B3}$ . Hence, it draws a very small AC current from the input voltage  $V_i$ . Therefore, the effective value of  $R_{\rm B3}$  has increased manifold. The effective value of  $R_{\rm B3}$  can be calculated by making use of Miller's effect:

$$R_{\rm B3(eff)} = \frac{R_{\rm B3}}{1 - A_{\rm v}} \tag{8.132}$$

As the value of voltage gain  $(A_v)$  is close to unity, value of  $R_{\rm B3(eff)}$  is very large. The effect of the voltage gain  $(A_v)$  approaching unity on the resistor  $R_{\rm B3(eff)}$  is referred to as bootstrapping. For unity value of  $A_v$  both ends of  $R_{\rm B3}$  increase by the same potential as if  $R_{\rm B3}$  were pulling it by its bootstraps.

#### **EXAMPLE 8.8**

Figure 8.39 shows a Darlington amplifier. The two transistors  $Q_1$  and  $Q_2$  are identical and the h-parameters for both the transistors are  $h_{ie}=1~k\Omega$ ,  $h_{fe}=100~$  and  $h_{oe}=40\times10^{-6}$  mhos. The values of the voltages  $V_{CC}=15~$ V,  $V_{BE1}=0.7~$ V and  $V_{BE2}=0.7~$ V. Determine the following:

Figure 8.39 | Example 8.8.

- (a) Quiescent values of DC voltages and currents.

#### Solution

1. The base bias current of the Darlington amplifier  $I_B$  is given by

$$\begin{split} I_{\mathrm{B}} &= \frac{V_{\mathrm{CC}} - V_{\mathrm{BE1}} - V_{\mathrm{BE2}}}{R_{\mathrm{B}} + (1 + h_{\mathrm{fe}})^2 R_{\mathrm{E}}} \\ &= \frac{15 - 0.7 - 0.7}{3 \times 10^6 + (101)^2 \times 400} \\ &= \frac{13.6}{3 \times 10^6 + 4.08 \times 10^6} = 1.92 \, \mu \mathrm{A} \end{split}$$

2. Emitter current of the Darlington amplifier is

$$I_{\text{E2}} = (1 + h_{\text{fe}})^2 I_{\text{B1}} = (101)^2 \times 1.92 \times 10^{-6} \,\mu\text{A} = 19.6 \,\text{mA}$$

- 3. The collector current of the Darlington amplifier  $I_C \cong I_E = 19.6$  mA.

- **4.** The collector–emitter voltage  $V_{\rm CE} = V_{\rm C} V_{\rm E} = 15 19.6 \times 10^{-3} \times 400 = 7.16 \, \rm V.$

5.

$$Z_{i} = R_{B} \left\| \frac{(1 + h_{fe})^{2} R_{E}}{1 + h_{oc} h_{fe} R_{E}} \right\|$$

$$= 3 \times 10^{6} \left\| \frac{(101)^{2} \times 400}{1 + 40 \times 10^{-6} \times 100 \times 400} \right\|$$

$$= 3 \times 10^{6} \left\| 1.57 \times 10^{6} = 1.03 \text{ M}\Omega \right\|$$

6.

$$Z_{o} \approx \frac{R_{s} + h_{ie}}{(1 + h_{fe})^{2}} + \frac{h_{ie}}{1 + h_{fe}}$$

$$= \frac{1 \times 10^{3} + 1 \times 10^{3}}{(101)^{2}} + \frac{1 \times 10^{3}}{101}$$

$$= 0.196 + 9.9$$

$$= 10.1 \Omega$$

7. Voltage gain  $A_{\nu}$  is given by

$$A_{v} = 1 - \frac{h_{ie}}{(1 + h_{fe})R_{E}}$$

$$= 1 - \frac{1 \times 10^{3}}{101 \times 400}$$

$$= 1 - 0.025$$

$$= 0.975$$

**8.** Current gain

$$A_i$$

is given by

$$A_i = \frac{R_B}{Z_i' + R_B} \times \left( \frac{(1 + h_{fe})^2}{1 + h_{oe} h_{fe} R_E} \right)$$

$$Z_i' = \frac{(1 + h_{fe})^2 R_E}{1 + h_{fe} h_{fe} R_F} = 1.57 \times 10^6$$

$$Z_{i}' = \frac{(1 + h_{fe})^{2} R_{E}}{1 + h_{oe} h_{fe} R_{E}} = 1.57 \times 10^{6}$$

Therefore,  $A_{i}$  is given by

$$A_{i} = \frac{3 \times 10^{6}}{3 \times 10^{6} + 1.57 \times 10^{6}} \times \frac{(101)^{2}}{1 + 40 \times 10^{-6} \times 100 \times 400}$$

$$= 0.66 \times 3923.46 = 2589.49$$

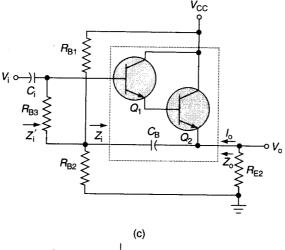

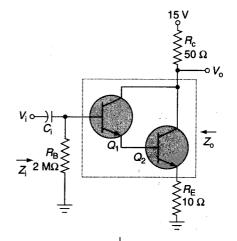

# 8.9 Cascode Amplifiers

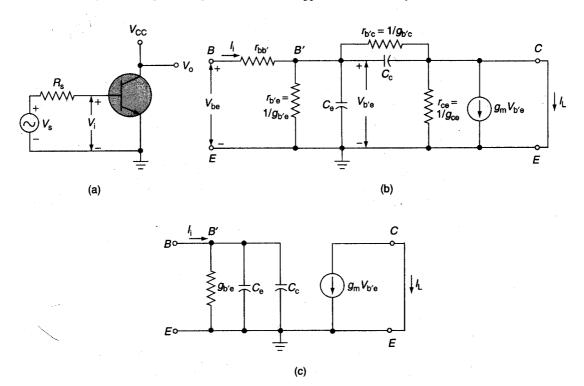

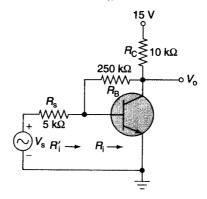

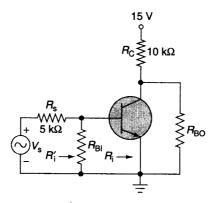

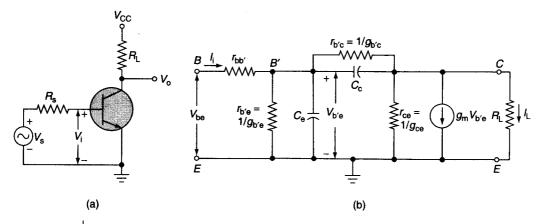

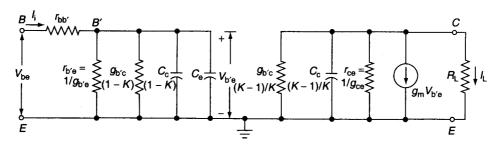

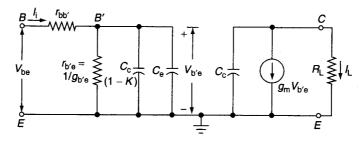

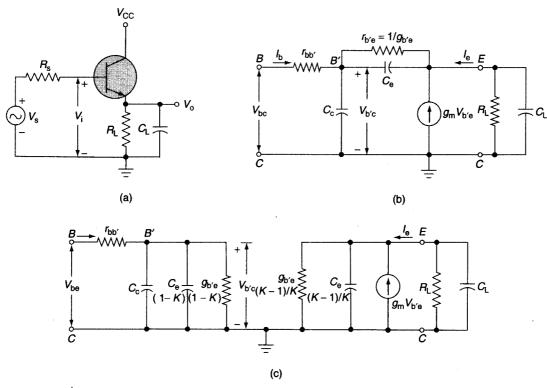

ascode amplifiers are two-stage amplifiers comprising a transconductance amplifier followed by a current buffer. They offer advantages like high input-output isolation, high input impedance and high output impedance. In a BJT cascode amplifier configuration, the common-emitter transistor amplifier is followed by a common-base transistor amplifier. Figure 8.40(a) shows the circuit diagram of a cascode amplifier wherein the transistor  $Q_1$  is configured as common-emitter amplifier and  $Q_2$  is configured as common-base amplifier. The common-base amplifier  $Q_2$  offers large bandwidth but its input impedance is low. Because of the low input impedance of  $Q_2$ , the voltage gain of  $Q_1$  is low. Therefore, the Miller's component of capacitance of transistor  $Q_1$  is small and the bandwidth of the cascode amplifier is wider than that for the common-emitter stage. Hence, cascode amplifiers are used for high-frequency applications.

In the case of an FET-based cascode amplifier, common-source amplifier is followed by common-gate amplifier as shown in Figure 8.40(b).

Figure 8.40 (a) BJT cascode amplifier; (b) FET cascode amplifier.

For the cascode amplifier circuit shown in Figure 8.41, determine the values of resistors  $R_{\rm E}$ ,  $R_{\rm 1}$  and  $R_{\rm 2}$  such that the operating point is  $I_{\rm CQ}=10$  mA and  $V_{\rm CEQ}=10$  V. Given that the value of  $\beta=100$  and  $V_{\rm BE}$  of each transistor is 0.7 V.

Figure 8.41 Example 8.9

#### **Solution**

- 1. DC voltage drop across the resistor  $R_C$  is given by  $470 \times 10 \times 10^{-3} = 4.7 \text{ V}$ .

- 2. Therefore, the voltage drop across the resistor  $R_{\rm E}$  is 15 4.7 10 10 (-15) = 30 24.7 = 5.3 V.

- 3. Value of resistor  $R_{\rm E}$  is approximately equal to  $5.3/10 \times 10^{-3} = 530 \ \Omega$ .

- **4.** Voltage at the base of transistor  $Q_1$  is given by -15 + 5.3 + 0.7 = -9 V.

- 5. For good bias stability, current through resistor  $R_2 >> I_{BQ1}$ . Value of  $R_2$  should not be so large such that this condition is not met and also it should not be too small to have an undue load on the power supply.

- **6.** Assume  $R_2 = 10 \text{ k}\Omega$ . Current through  $R_2$  is  $9/(10 \times 10^3) = 0.9 \text{ mA}$ .

- 7. Current through resistor  $R_1 = 0.9 \times 10^{-3} 10 \times 10^{-3}/100 = 0.9 \times 10^{-3} 10 \times 10^{-5} = 0.89 \times 10^{-3} = 0.89 \text{ mA}.$

- **8.** Voltage drop across  $R_1$  is 15 9 = 6 V.

- **9.** Value of resistor  $R_1 = 6/(0.89 \times 10^{-3}) = 6.74 \text{ k}\Omega$ .

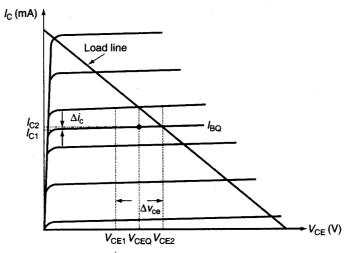

# 8.10 Low-Frequency Response of Amplifiers

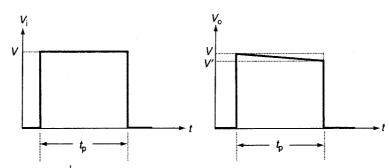

As discussed in the earlier part of the chapter, the frequency of the applied input signal has a great effect on the response of the amplifier. The low-frequency response is limited by the coupling and the bypass capacitors as they can no longer be considered as short circuits. The high-frequency response is affected by the stray capacitive elements associated with the active device. Moreover, as the number of amplifier stages increases, the low- and the high-frequency response gets further limited. In this section, we will discuss the low-frequency response of the BJT and FET amplifiers. This is followed by a discussion on the effect of cascading amplifier stages on the overall frequency response of the amplifier in the next section. The high-frequency response of amplifiers is discussed in Chapter 9.

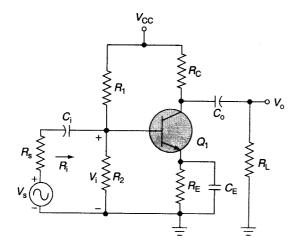

#### Low-Frequency Response of BJT Amplifiers

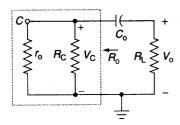

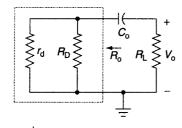

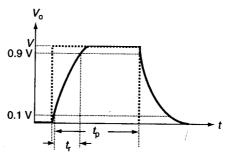

In the low-frequency region of operation, a BJT or an FET amplifier's response is affected by the R-C combinations formed by the network capacitors including the coupling and bypass capacitors and the network resistive elements. In this section we discuss the effect of these capacitors on the low-frequency response of the voltage-divider BJT amplifier configuration. The results can be generalized to any transistor configuration. Figure 8.42 shows the voltage-divider BJT amplifier configuration.  $C_i$  is the input-coupling capacitor and is connected between the applied input source and the active device.  $C_{\rm o}$  is the output-coupling capacitor and is connected between the output of the active device and the load.

#### Effect of Input Coupling Capacitor

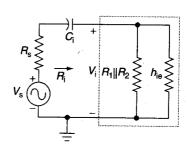

The capacitor  $C_i$  forms an RC network as shown in Figure 8.43.  $R_i$  is the input resistance of the amplifier as seen by the source and is given by parallel combination of  $R_1$ ,  $R_2$  and  $h_i$ :

$$R_{i} = R_{i} \| R_{2} \| b_{ic} \tag{8.133}$$

The voltage  $V_i$  applied to the input of the active device is calculated by using the voltage-divider rule. Therefore, voltage  $V_i$  is given by

$$V_{i} = \frac{R_{i}}{R_{s} + R_{i} - jX_{C}} \times V_{s} \tag{8.134}$$

$V_{i} = \frac{R_{i}}{R_{s} + R_{i} - jX_{C_{s}}} \times V_{s}$ At mid- and high frequencies the reactance of capacitors  $C_{i}$  and  $C_{o}$  will be sufficiently small to permit a short-circuit approximation. Therefore, the input voltage at mid-band frequencies ( $V_{\text{i-mid}}$ ) is given by

$$V_{i-\text{mid}} = \frac{R_i}{R_s + R_i} \times V_s \tag{8.135}$$

$V_{\text{i-mid}} = \frac{R_{\text{i}}}{R_{\text{s}} + R_{\text{i}}} \times V_{\text{s}}$  The cut-off frequency established by the capacitor  $C_{\text{i}}$  is given by

$$f_{\rm LC_i} = \frac{1}{2\pi (R_i + R_s)C_i} \tag{8.136}$$

$f_{\rm LC_i} = \frac{1}{2\pi (R_{\rm i} + R_{\rm s})C_{\rm i}} \tag{8.136}$  At  $f_{\rm LC_i}$  the voltage  $V_{\rm i}$  will be 0.707 times the voltage  $V_{\rm i-mid}$  assuming that  $C_{\rm i}$  is the only capacitive element effecting the low-frequency response.

Figure 8.42 Voltage-divider BJT amplifier configuration.

Figure 8.43 Determining the effect of inputcoupling capacitor on the lowfrequency response.

#### Effect of the Output Coupling Capacitor

The output coupling capacitor  $(C_0)$  is connected between the output of the active device and the load. Figure 8.44 shows the simplified configuration highlighting the effect of  $C_0$  on the low-frequency response of the amplifier.  $R_0$  is the total output resistance and is given by

$$R_{o} = R_{C} \parallel r_{o} \cong R_{C} \tag{8.137}$$

The cut-off frequency as established by  $C_0$  is given by

$$f_{\rm LC_o} = \frac{1}{2\pi (R_{\rm o} + R_{\rm L})C_{\rm o}} \cong \frac{1}{2\pi (R_{\rm C} + R_{\rm L})C_{\rm o}}$$

(8.138)

The output voltage  $V_o$  will be 70.7% of its mid-band value at the frequency  $f_{LC_o}$  assuming that  $C_o$  is the only capacitive element controlling the low-frequency response.

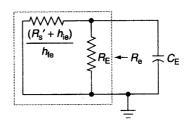

#### Effect of Bypass Capacitor

Figure 8.45 shows the network as seen by the bypass capacitor  $C_{\rm E}$ . The value of the equivalent resistance  $R_{\rm E}$  is given by

$$R_{\rm e} = R_{\rm E} \left[ [(R_{\rm s}' + h_{\rm ie})/h_{\rm fe}] \right] \tag{8.139}$$

where

$$R_{s}' = R_{s} \| R_{1} \| R_{2}$$

The cut-off frequency as established by resistance  $R_{\rm E}$  and capacitor  $C_{\rm E}$  is given by

$$f_{\rm LC_E} = \frac{1}{2\pi R_{\rm e} C_{\rm E}} \tag{8.140}$$

The effect of bypass capacitor  $C_{\rm E}$  can be explained qualitatively by considering that at low frequencies the capacitor  $C_{\rm E}$  acts like an open circuit and whole of the resistor  $R_{\rm E}$  appears in the gain equation, resulting in minimum value of gain. As the frequency increases, the reactance of the capacitor  $C_{\rm E}$  decreases resulting in decrease in the value of parallel impedance of resistor  $R_{\rm E}$  and capacitor  $C_{\rm E}$ . The gain is maximum when the impedance of the capacitor  $C_{\rm F}$  reduces so much that it can be considered as a short circuit.

It may be mentioned here that the input and the output coupling capacitors and the bypass capacitors effect only the low-frequency response. At the mid-band frequency range they are considered as short-circuit equivalent and do not affect the gain at these frequencies. If the cut-off frequencies offered by them are far apart then the highest cut-off frequency due to the three capacitors essentially determines the cut-off frequency of the entire system. If the cut-off frequencies are near to each other then the effect will be to raise

Figure 8.44 Determining the effect of output coupling capacitor on the low-frequency response.

Figure 8.45 Determining the effect of bypass capacitor on the low-frequency response.

the lower cut-off frequency of the entire system, that is, there is an interaction between the capacitive elements resulting in increased lower cut-off frequency for the entire system.

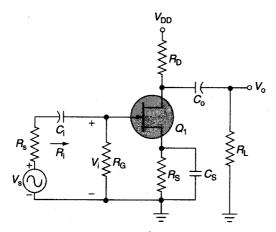

#### Low-Frequency Response of FET Amplifiers